# TOWARD HIGH PERFORMANCE AND ENERGY EFFICIENCY ON MANY-CORE ARCHITECTURES

by

Elkin Garcia

A dissertation submitted to the Faculty of the University of Delaware in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Summer 2014

© 2014 Elkin Garcia All Rights Reserved

# TOWARD HIGH PERFORMANCE AND ENERGY EFFICIENCY ON MANY-CORE ARCHITECTURES

by

Elkin Garcia

Approved: \_\_\_\_\_

Kenneth E. Barner, Ph.D. Chair of the Department of Electrical and Computer Engineering

Approved: \_

Babatunde A. Ogunnaike, Ph.D. Dean of the College of Engineering

Approved: \_\_\_\_\_

James G. Richards, Ph.D. Vice Provost for Graduate and Professional Education

I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: \_\_\_\_\_

Guang R. Gao, Ph.D. Professor in charge of dissertation

I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: \_

Xiaoming Li, Ph.D. Member of dissertation committee

I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: \_\_\_\_\_

Hui Fang, Ph.D. Member of dissertation committee

I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: \_

Jingyi Yu, Ph.D. Member of dissertation committee To my mom and grandma:

For teaching me by example to do the right things and to do my best effort no matter the difficulties.

#### ACKNOWLEDGEMENTS

Approaching the end of this journey, there is so much people to acknowledge. First, I want to thank my family, specially my mom. They have encouraged me to follow my dreams and they have been supportive during all these years far from home. I also want to thank Prof. Fernando Lozano, he encouraged me to explore the world and he showed me the path for pursuing a Ph.D since I was an undergrad.

During these years in the US, I have met so many people. I want to deeply express my appreciation to Prof. Guang R. Gao, he has guided me and taught me on many aspects of life during these years. He also gave me the freedom to explore and progress on my research interest. I want to thank my dissertation committee for your comments and suggestions in order to improve the quality of this work.

I am so thankful to be part of the Computer Architecture and Parallel System Laboratory (CAPSL). All CAPSL members (It is a very long list) are very talented and I enjoyed not just the academic and technical discussions but also the opportunity to learn about their culture and personal life. I particularly want to mention my mentors, close collaborators and friends: Dr. Ioannis Venetis, Dr. Joseph Manzano, Dr. Daniel Orozco, Sunil Shrestha, Robert Pavel, Jaime Arteaga and Sergio Pino. I am also grateful from the close collaboration I had with ET International and particularly with Dr. Rishi Khan.

During these years I was also surrounded by very good friends that make my life pleasant in the US. I was able to share with many different cultures and nationalities. It enhanced my Ph.D. experience. I particularly enjoyed all the support from a close group of friends known as 'Los Cheveres'.

Finally, I want to thank all the staff in the ECE Department at U. of Delaware for their valuable guidance and help through all the stages I had to pass during these years as an International Ph.D student. Particularly, Kathy Forwood has been extremely helpful from the first day I joined U. of Delaware.

### TABLE OF CONTENTS

| LI | LIST OF TABLES       xii         LIST OF FIGURES       xiii         ABSTRACT       xvii |                                                                                                                    |  |  |  |  |  |

|----|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| C  | hapter                                                                                  |                                                                                                                    |  |  |  |  |  |

| 1  | I INTRODUCTION                                                                          |                                                                                                                    |  |  |  |  |  |

|    | 1.1Frequency Wall                                                                       | $     \begin{array}{c}       1 \\       2 \\       3 \\       3 \\       4 \\       4 \\       6     \end{array} $ |  |  |  |  |  |

| 2  | AN OVERVIEW OF DATAFLOW         2.1         The Static Model                            | <b>7</b><br>8                                                                                                      |  |  |  |  |  |

|    | <ul> <li>2.2 The Unraveling Interpreter</li></ul>                                       | 9<br>9<br>10                                                                                                       |  |  |  |  |  |

| 3  | PROBLEM FORMULATION                                                                     | 14                                                                                                                 |  |  |  |  |  |

| 4  | AN INNOVATIVE MANY-CORE ARCHITECTURE                                                    | 16                                                                                                                 |  |  |  |  |  |

|    | <ul> <li>4.1 Memory Hierarchy</li></ul>                                                 | 17<br>18                                                                                                           |  |  |  |  |  |

| 5  | STATIC OPTIMIZATIONS IN THE CONTEXT OF<br>MANY-CORE ARCHITECTURES                       | 20                                                                                                                 |  |  |  |  |  |

|    | 5.1 Classic Matrix Multiplication Algorithms                                            | 22                                                                                                                 |  |  |  |  |  |

|   | 5.2                                                                                       | Propo                                                           | sed Matrix Multiplication Algorithm                                                             | 23                   |  |  |

|---|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------|--|--|

|   |                                                                                           | 5.2.1<br>5.2.2<br>5.2.3                                         | Work DistributionMinimization of High Cost Memory OperationsArchitecture Specific Optimizations | 23<br>24<br>27       |  |  |

|   | 5.3                                                                                       | Exper                                                           | imental Evaluation                                                                              | 28                   |  |  |

| 6 | THE PROBLEM OF STATIC TECHNIQUES AND THE RISING<br>OF DYNAMIC OPTIMIZATIONS FOR MANY-CORE |                                                                 |                                                                                                 |                      |  |  |

|   | AR                                                                                        | CHITI                                                           | ECTURES                                                                                         | 32                   |  |  |

|   | $6.1 \\ 6.2 \\ 6.3 \\ 6.4$                                                                | Static<br>Percol                                                | ation                                                                                           | 34<br>37<br>38<br>41 |  |  |

|   |                                                                                           | $\begin{array}{c} 6.4.1 \\ 6.4.2 \\ 6.4.3 \\ 6.4.4 \end{array}$ | Fine-grained task partitioning                                                                  | 41<br>43<br>44<br>47 |  |  |

|   | 6.5                                                                                       | Dynar                                                           | nic Percolation                                                                                 | 48                   |  |  |

|   |                                                                                           | $6.5.1 \\ 6.5.2$                                                | Computation of one block $C_{i,j}$                                                              | $51\\52$             |  |  |

|   | 6.6                                                                                       | Exper                                                           | imental Evaluation                                                                              | 53                   |  |  |

|   |                                                                                           | 6.6.1<br>6.6.2<br>6.6.3<br>6.6.4                                | Experimental Testbed                                                                            | 53<br>54<br>55<br>59 |  |  |

| 7 | AR                                                                                        | CHITI                                                           | MANCE MODELING OF MANY-CORE<br>ECTURES UNDER DYNAMIC SCHEDULING AND<br>CE CONSTRAINTS           | 61                   |  |  |

|   | $7.1 \\ 7.2$                                                                              |                                                                 | ation                                                                                           | 63<br>67             |  |  |

|   |                                                                                           | 7.2.1                                                           | The Codelet Execution Model                                                                     | 68                   |  |  |

|     | 7.2.2          | Petri Ne                                              | ets                                                                                                                    | 68                         |  |

|-----|----------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------|--|

| 7.3 | Soluti         | on Metho                                              | d                                                                                                                      | 70                         |  |

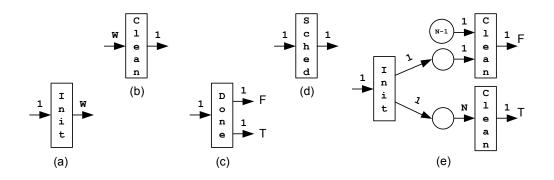

|     | 7.3.1          | Basic ac                                              | etors in timed Petri nets                                                                                              | 71                         |  |

|     |                | $7.3.1.1 \\ 7.3.1.2 \\ 7.3.1.3 \\ 7.3.1.4 \\ 7.3.1.5$ | Init                                                                                                                   | 71<br>71<br>71<br>72<br>72 |  |

|     | 7.3.2          | Expressi                                              | ing concurrency                                                                                                        | 73                         |  |

|     |                | 7.3.2.1<br>7.3.2.2                                    | Parallel for loop - On Chip Matrix Multiplication<br>Serial for loop - Computing a whole block from off-chip<br>memory | 73<br>74                   |  |

|     | 7.3.3          | -                                                     | entation of Performance Optimizations and Modeling of<br>e Constraints                                                 | 75                         |  |

|     |                | $7.3.3.1 \\ 7.3.3.2 \\ 7.3.3.3 \\ 7.3.3.4$            | Double Buffering and Pipelining                                                                                        | 75<br>76<br>77<br>78       |  |

|     | 7.3.4          |                                                       | ology for generation of timed Petri nets with resource ation conditions                                                | 79                         |  |

| 7.4 | Experiments    |                                                       |                                                                                                                        |                            |  |

|     | 7.4.1          | Verificat                                             | tion of Model and Evaluation of Performance ations                                                                     | 82                         |  |

|     |                | 7.4.1.1<br>7.4.1.2                                    | Dense Matrix Multiplication                                                                                            | 82<br>86                   |  |

|     | 7.4.2<br>7.4.3 | -                                                     | lation of Results on Similar Architectures                                                                             | 88<br>90                   |  |

| 8                          | PO         | WER .                   | AWARE TILING TRANSFORMATIONS                                                                                   | 95                                        |

|----------------------------|------------|-------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------|

|                            | 8.1<br>8.2 | 0.                      | y Consumption Model on a Many-Core Architecture Techniques for Energy Efficient Applications                   | 96<br>98                                  |

|                            |            | 8.2.1<br>8.2.2          | Matrix Multiplication                                                                                          | $\begin{array}{c} 100 \\ 101 \end{array}$ |

|                            | 8.3        | Exper                   | imental Evaluation                                                                                             | 103                                       |

|                            |            | $8.3.1 \\ 8.3.2$        | Evaluation of the Energy Consumption Model                                                                     | $\begin{array}{c} 103 \\ 107 \end{array}$ |

| 9                          | EN         | ERGY                    | OPTIMIZATIONS IN THE CONTEXT OF                                                                                |                                           |

|                            | MA         | NY-C                    | ORE ARCHITECTURES                                                                                              | 111                                       |

|                            | 9.1<br>9.2 |                         | octorization                                                                                                   | 112<br>114                                |

|                            |            | 9.2.1<br>9.2.2<br>9.2.3 | Energy Aware Tiling design                                                                                     | 115<br>118<br>119                         |

|                            | 9.3        | Exper                   | imental Evaluation                                                                                             | 121                                       |

| 10                         | -          | -                       | FFS BETWEEN PERFORMANCE AND ENERGY<br>ATIONS FOR MANY-CORE ARCHITECTURES                                       | 127                                       |

|                            | 10.1       | Optim                   | izing for Energy is More Difficult than Optimizing for                                                         |                                           |

|                            | 10.0       |                         |                                                                                                                | 127                                       |

|                            |            |                         | offs between Performance and Energy Optimizations e of Study for Performance and Energy Consumption Trade offs | 129<br>131                                |

| 11                         | RE         | LATEI                   | D WORK AND EXTENSIONS                                                                                          | 135                                       |

| 12 SUMMARY AND CONCLUSIONS |            |                         |                                                                                                                | 141                                       |

| B                          | IBLI       | OGRA                    | PHY                                                                                                            | 148                                       |

# Appendix

| Α | CO  | PYRIGHT INFORMATION              | 166 |

|---|-----|----------------------------------|-----|

|   | A.1 | Copy of the Licensing Agreements | 166 |

### LIST OF TABLES

| 5.1 | Number of memory operation for different tiling strategies                 | 27  |

|-----|----------------------------------------------------------------------------|-----|

| 6.1 | Summary of Previous Results of MM on C64                                   | 34  |

| 8.1 | $E_d$ consumed by memory operations for MM                                 | 102 |

| 8.2 | $E_d$ consumed by memory operations for FDTD $\ldots \ldots \ldots \ldots$ | 103 |

| 8.3 | Energy Coefficients $e$ and $R^2$                                          | 107 |

### LIST OF FIGURES

| 1.1 | Processor Frequency over time                                                                                                                                                                     | 2  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Number of Transistors over time                                                                                                                                                                   | 5  |

| 4.1 | C64 Chip Architecture                                                                                                                                                                             | 16 |

| 4.2 | Memory Hierarchy of C64                                                                                                                                                                           | 17 |

| 5.1 | Implementation of sequences for traversing tiles in one block of ${\cal C}~$ .                                                                                                                    | 26 |

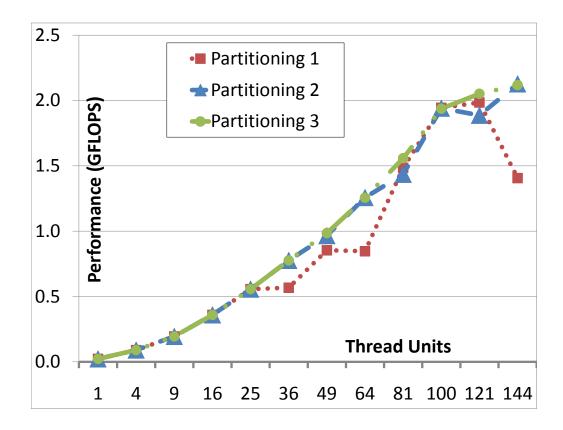

| 5.2 | Different Partition Schemes vs. Number of Threads Units. Matrix Size $100 \times 100 \dots \dots$ | 29 |

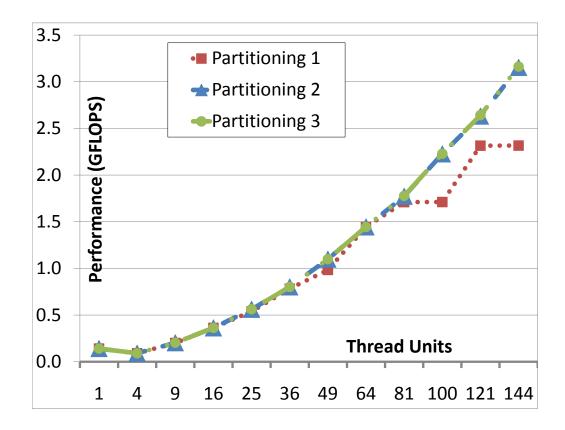

| 5.3 | Different Partition Schemes vs. Number of Threads Units. Matrix Size $488 \times 488 \ldots$                                                                                                      | 30 |

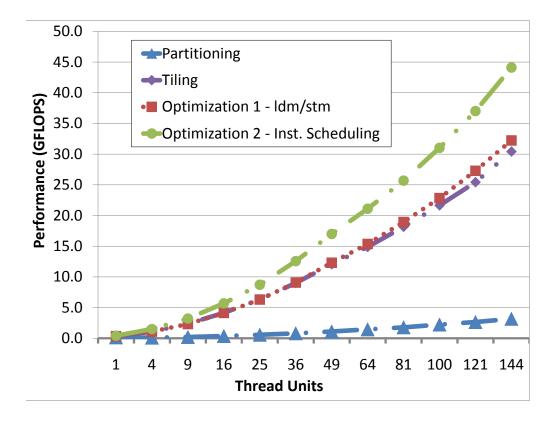

| 5.4 | Impact of each optimization on the performance of MM using $m = 488 \dots \dots$                  | 31 |

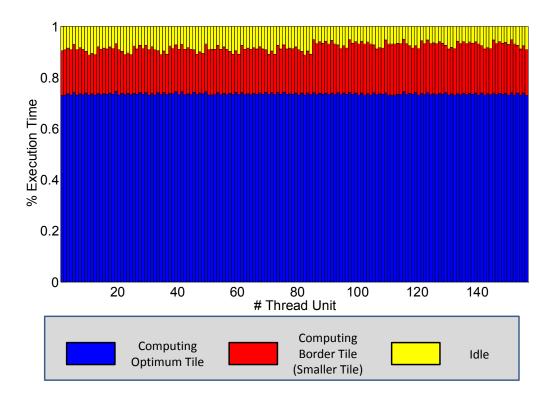

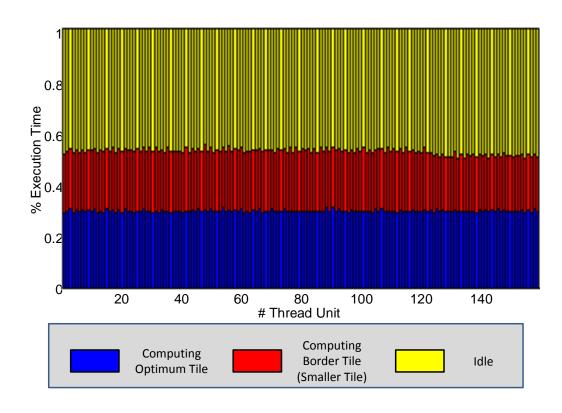

| 6.1 | Workload Distribution for a MM of size $488 \times 488 \ldots \ldots \ldots$                                                                                                                      | 35 |

| 6.2 | Workload Distribution for a MM of size $192 \times 192 \dots \dots \dots$                                                                                                                         | 36 |

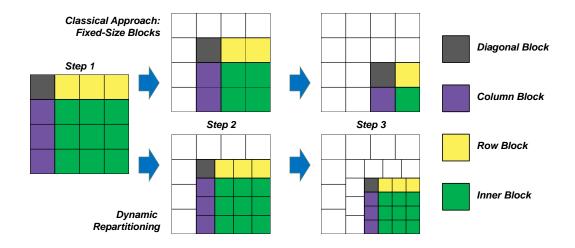

| 6.3 | Problem of static partition in Matrix Multiplication                                                                                                                                              | 38 |

| 6.4 | Algorithm for computing a tile of $C$ with size $L_1 \times L_2  \ldots  \ldots$                                                                                                                  | 40 |

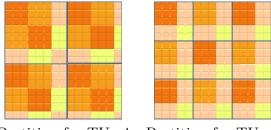

| 6.5 | Partition Schemes for a matrix C of $15\times15$ with tiles of $3\times3$                                                                                                                         | 42 |

| 6.6 | Code Fragment for a DS implementation                                                                                                                                                             | 45 |

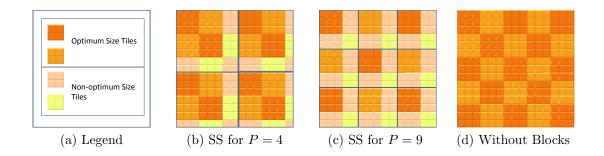

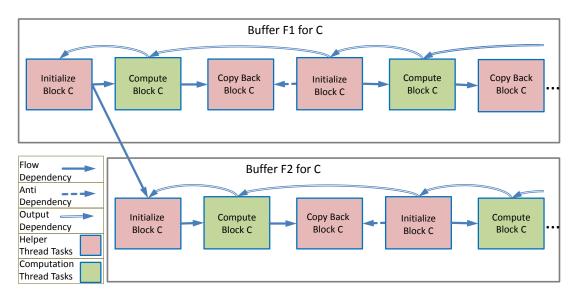

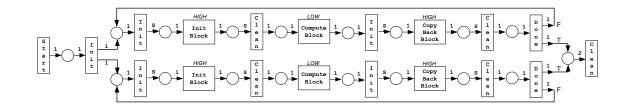

| 6.7 | Tasks for computing one block $C_{i,j} \in C$                                                                                                                                                     | 49 |

| 6.8 | Dynamic Percolation for Computation of one block $C_{i,j}$                                                                                                                                        | 51 |

| 6.9  | Dynamic Percolation for Computation of matrix $C$                                                        | 52 |

|------|----------------------------------------------------------------------------------------------------------|----|

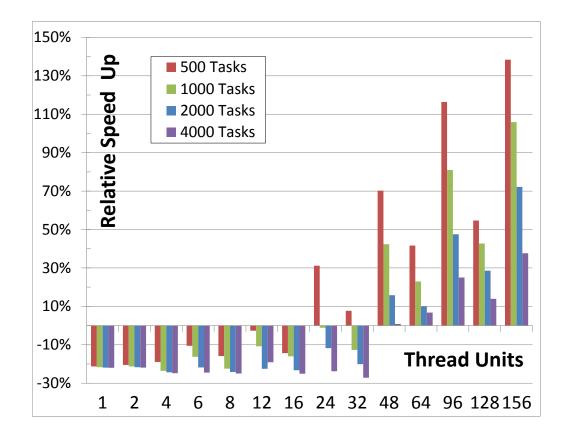

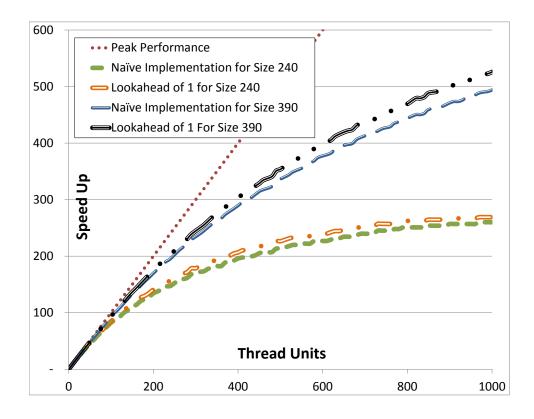

| 6.10 | Relative Speed Up of DS vs. SS                                                                           | 55 |

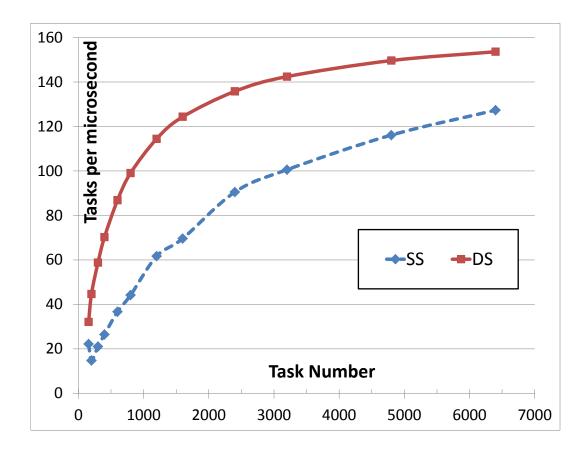

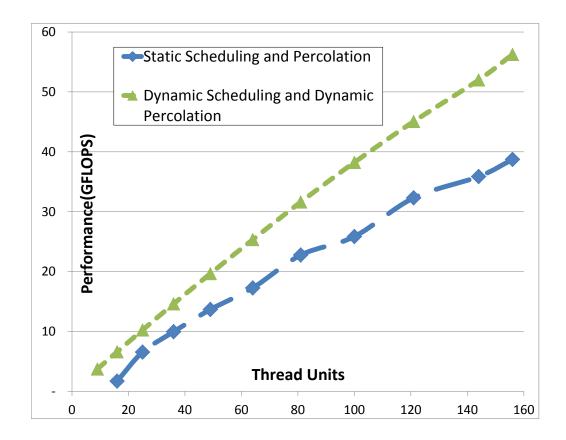

| 6.11 | Scalability for 156 PEs                                                                                  | 56 |

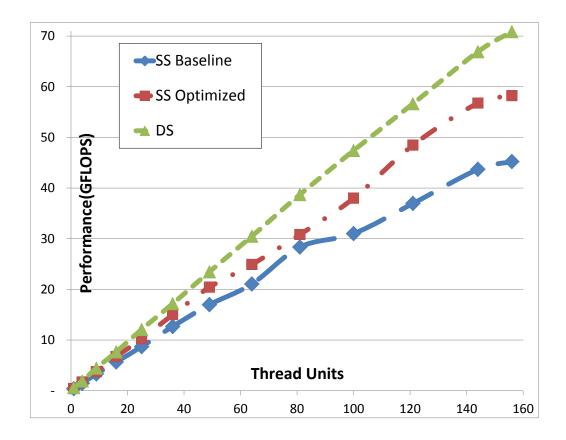

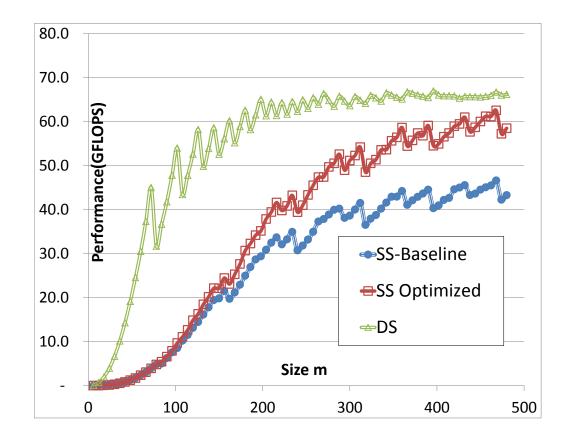

| 6.12 | Performance for a DMM of size $486 \times 486$                                                           | 57 |

| 6.13 | Scalability for a DMM with 144 PEs                                                                       | 58 |

| 6.14 | Scalability for a DMM of size $6480 \times 6480$                                                         | 59 |

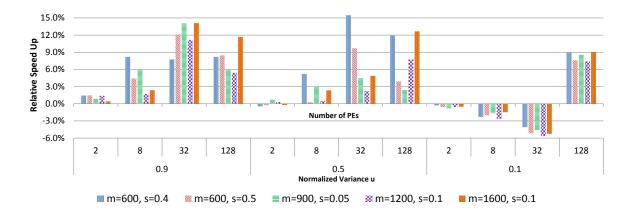

| 6.15 | Relative Speed Up of DS vs. SS for SpVMM                                                                 | 60 |

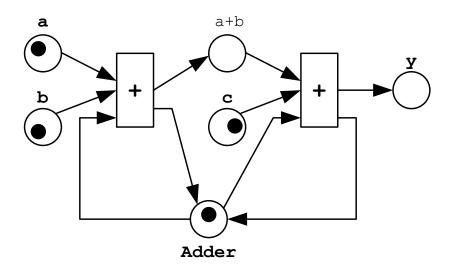

| 7.1  | A Petri net model of the computation of $y = a + b + c$ in a system<br>with only one adder.              | 70 |

| 7.2  | Basic actors in Timed Petrinets                                                                          | 72 |

| 7.3  | Pseudo algorithm for Dense Matrix Multiplication                                                         | 73 |

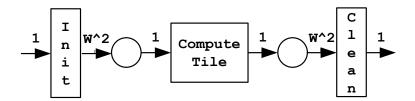

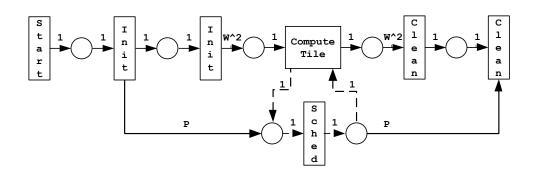

| 7.4  | Petri net model for on-chip matrix multiplication                                                        | 74 |

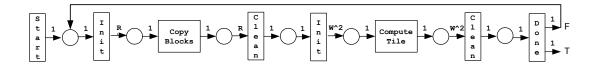

| 7.5  | Petri net model for off-chip matrix multiplication of a single block .                                   | 75 |

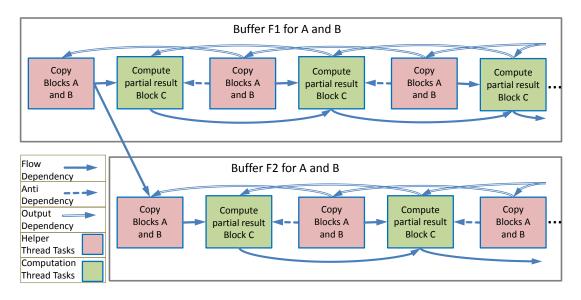

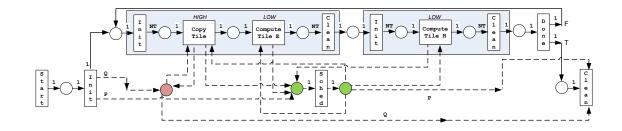

| 7.6  | Petri net model with resource constraints for optimized off-chip matrix multiplication of a single block | 76 |

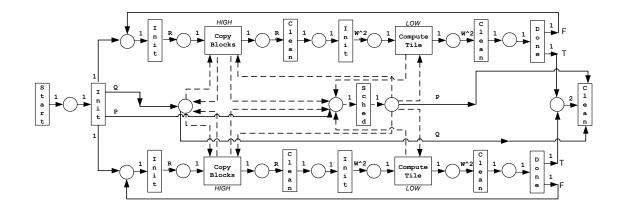

| 7.7  | Petri net model for optimized off-chip matrix multiplication $\ldots$ .                                  | 78 |

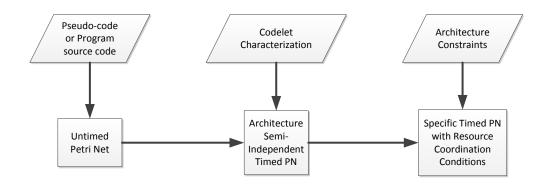

| 7.8  | Methodology for generation of a Timed Petri net model with resource coordination conditions              | 79 |

| 7.9  | Pseudo algorithm for Finite Difference Time Domain $\ldots \ldots \ldots$                                | 80 |

| 7.10 | Petri net model for Finite Difference Time Domain                                                        | 81 |

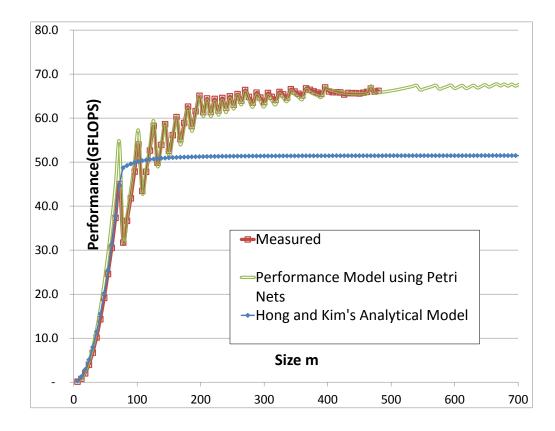

| 7.11 | Dense Matrix Multiplication optimized for On-Chip Memory                                                 | 83 |

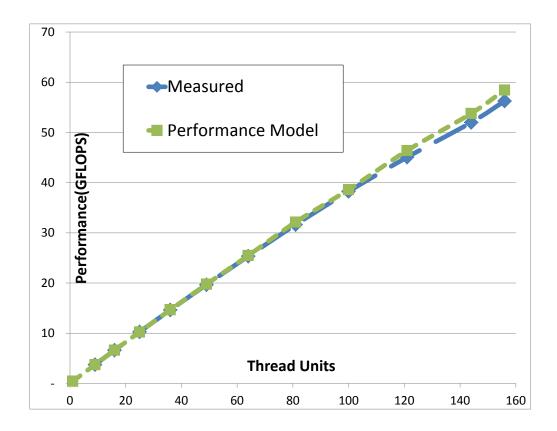

| 7.12 | On-Chip Memory Dense Matrix Multiplication                                                               | 84 |

| 7.13 | Off-Chip Memory Dense Matrix Multiplication with Double Buffering                                        | 85 |

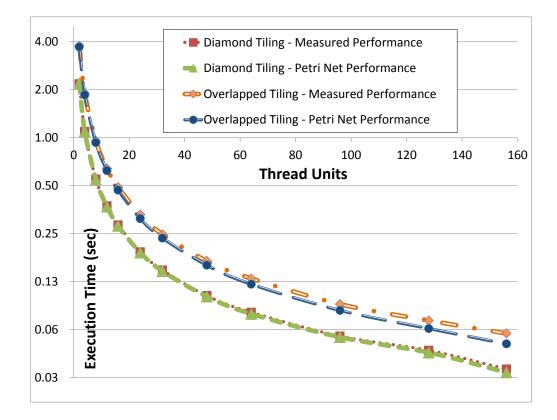

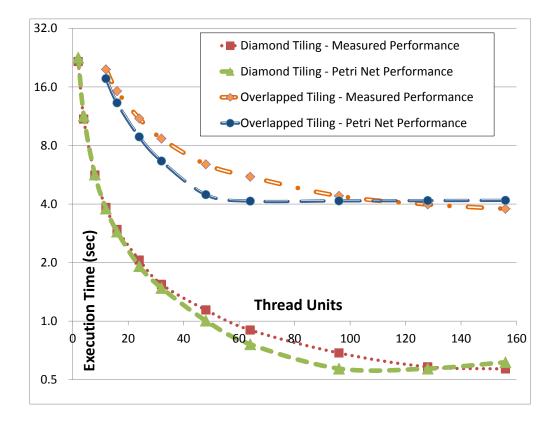

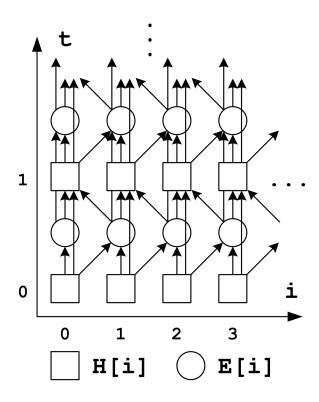

| 7.14 | FDTD in 1 Dimension                                                                                                                                                                          | 87  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.15 | FDTD in 2 Dimensions                                                                                                                                                                         | 88  |

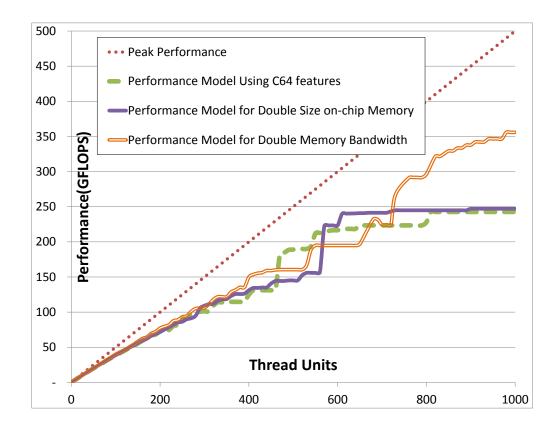

| 7.16 | Study of New Features on Dense Matrix Multiplication                                                                                                                                         | 89  |

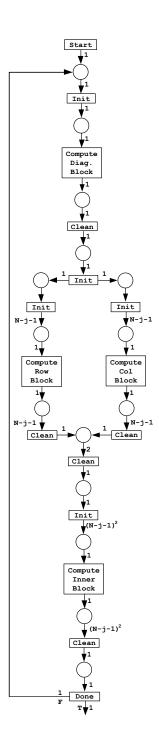

| 7.17 | Petri Net Modeling of LU Factorization                                                                                                                                                       | 91  |

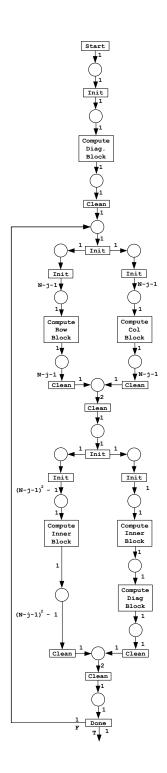

| 7.18 | Petri Net Modeling of LU Factorization with Lookahead of $1\ .\ .\ .$                                                                                                                        | 92  |

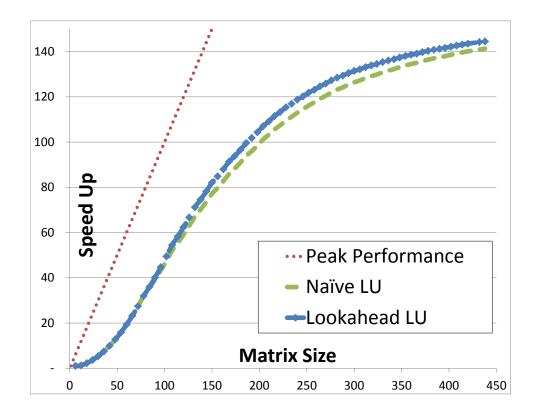

| 7.19 | Predicted Results for LU Factorization - Speed-Up For 156 Threads<br>Relative to Matrix Size                                                                                                 | 93  |

| 7.20 | Predicted Results for LU Factorization - Speed-Up Relative to the Number of Threads                                                                                                          | 94  |

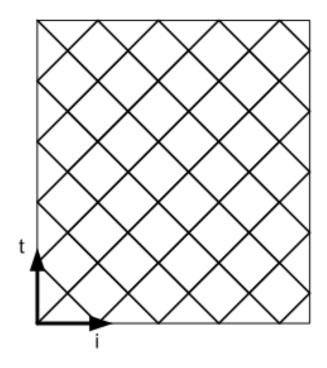

| 8.1  | DDG for FDTD 1D                                                                                                                                                                              | 103 |

| 8.2  | Diamond Tiling                                                                                                                                                                               | 104 |

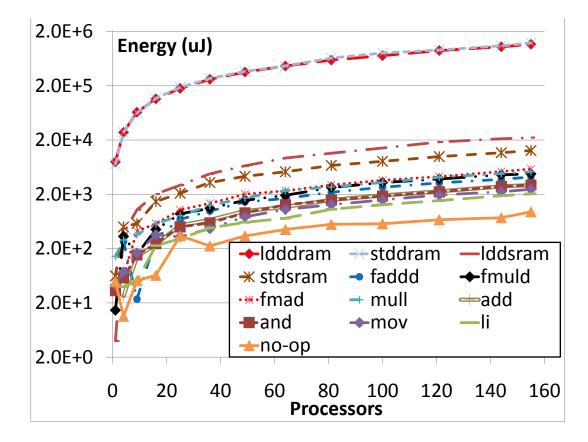

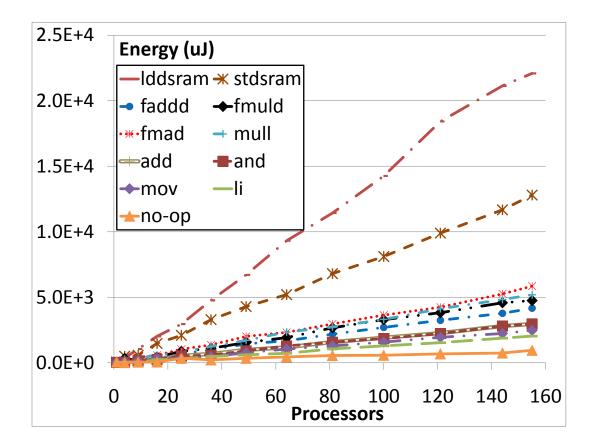

| 8.3  | Overall comparison of selected ISA                                                                                                                                                           | 105 |

| 8.4  | Comparison for On-chip Mem. Op., FPU Op. and Integer/Logical Op.                                                                                                                             | 106 |

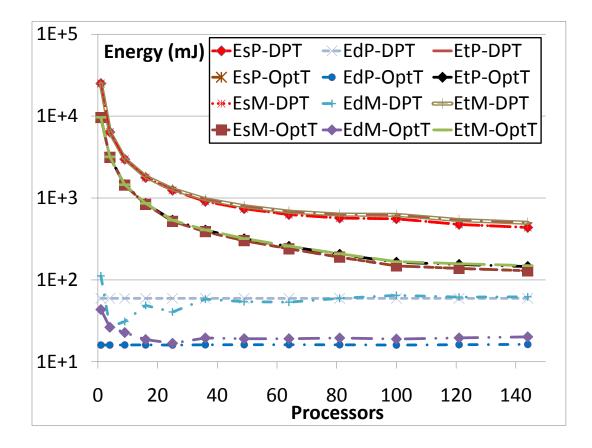

| 8.5  | Energy consumption vs Predicted model $P$ and Measured $M$ for MM with $m = 300 \dots \dots$ | 109 |

| 8.6  | Energy consumption vs Predicted model $P$ and Measured $M$ for FDTD with $m = 100k$ and $q = 500 \dots \dots \dots \dots \dots \dots \dots \dots \dots$                                      | 110 |

| 9.1  | Progress in each step of LU Factorization                                                                                                                                                    | 114 |

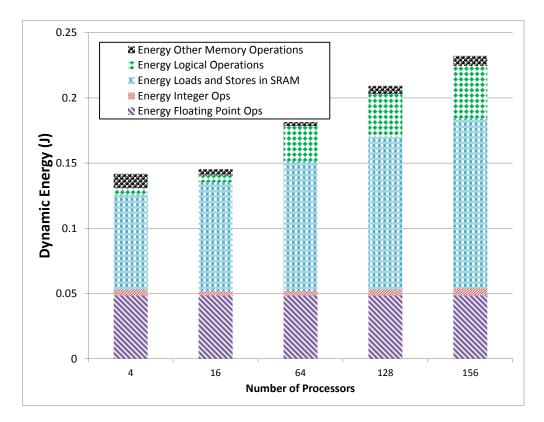

| 9.2  | Dynamic Energy Distribution for LU factorization of $840\times840$ $$                                                                                                                        | 115 |

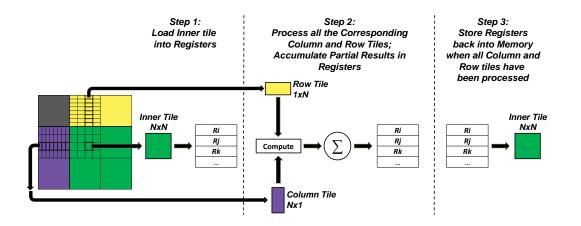

| 9.3  | Optimum Energy-Aware Tiling for an Inner Block                                                                                                                                               | 118 |

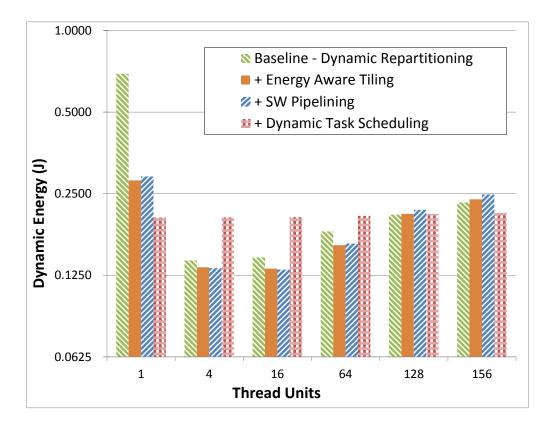

| 9.4  | Dynamic Energy vs. Thread Units for a matrix of $840\times840$                                                                                                                               | 122 |

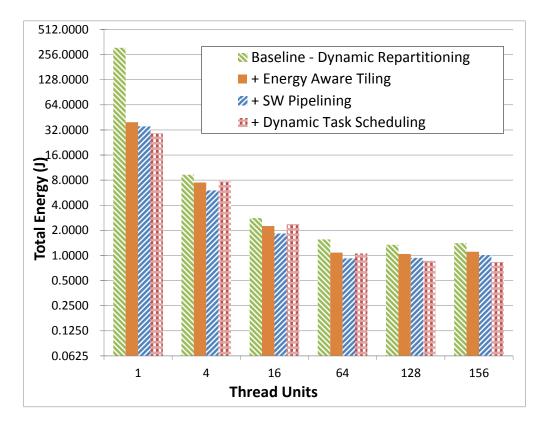

| 9.5  | Total Energy vs. Thread Units for a matrix of $840 \times 840$                                                                                                                               | 123 |

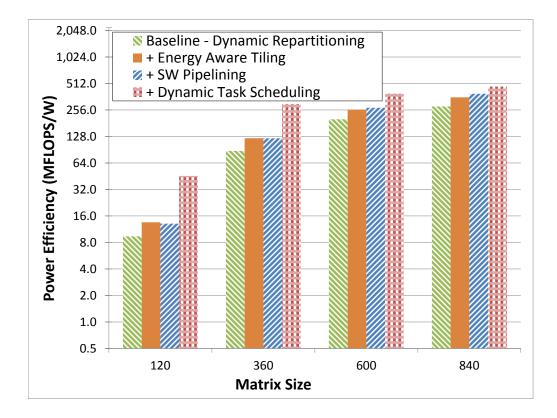

| 9.6  | Power Eff. vs. Matrix Size for $TU = 156$                                                                                                                                                    | 124 |

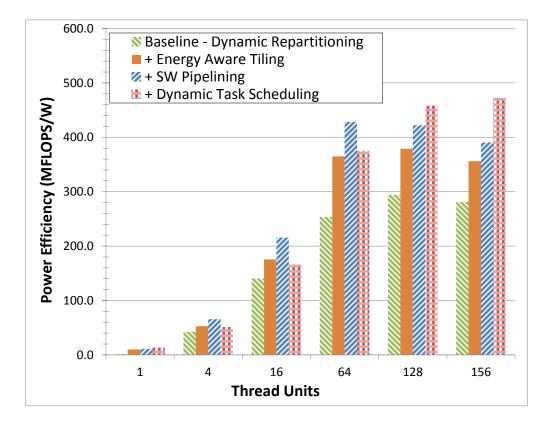

| 9.7  | Power Eff. vs. TUs for Matrix Size $840 \times 840$                                                                     | 125 |

|------|-------------------------------------------------------------------------------------------------------------------------|-----|

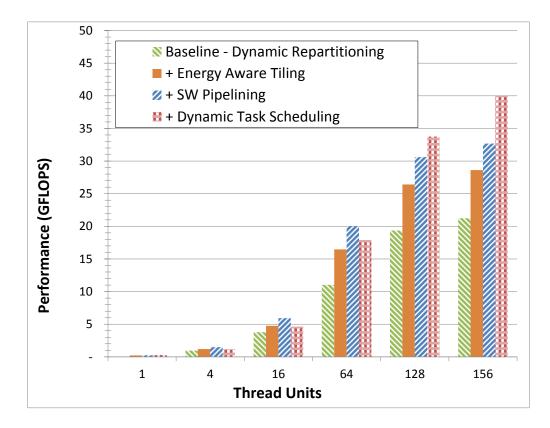

| 9.8  | Performance vs. TUs for Matrix Size $840 \times 840$                                                                    | 126 |

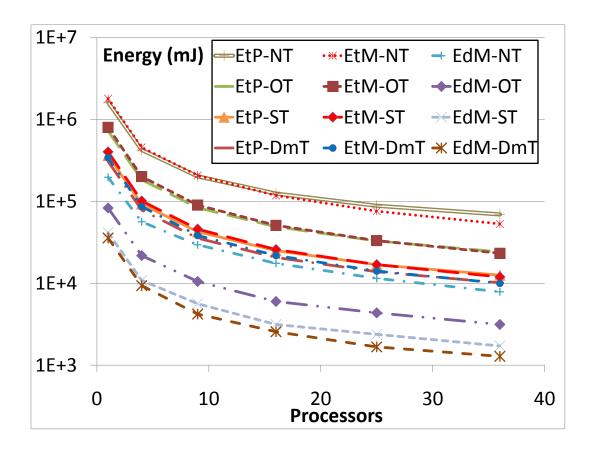

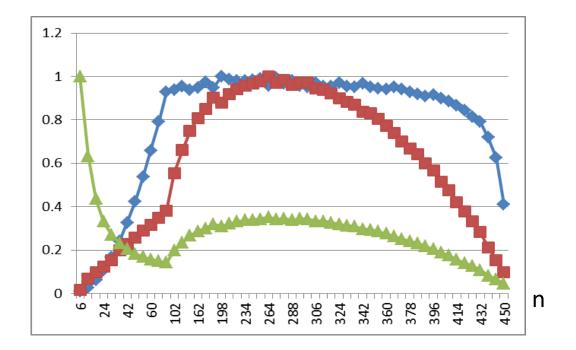

| 10.1 | Projection of Performance and Dynamic Energy vs. size of the rectangular tiling for Matrix Multiplication               | 132 |

| 10.2 | Normalized Performance, Dynamic Energy and Total Energy vs. size<br>of the rectangular tiling for Matrix Multiplication | 133 |

#### ABSTRACT

Recent attempts to build peta-scale and exa-scale systems have precipitated the development of new processor with hundreds, or even thousands, of independent processing units. This many-core era have brought new challenges on several fields including computer architecture, algorithm design and operating systems among others. Addressing these challenges implies new paradigms over some well-established methodologies for traditional serial architectures.

These new many-core architectures are characterized not only by the large amount of processing elements but also by the large number and heterogeneity of resources. This new environment has prompted the development of new techniques that seek finer granularity and a greater interplay in the sharing of resources. As a result, several elements of computer systems and algorithm design need to be re-evaluated under these new scenarios; it includes runtime systems, scheduling schemes and compiler transformations.

The number of transistors on a chip continues to grow following Moore's law, but single processor architectures manufactured by main vendors in the late 90's were in trouble taking advantage of the increasing number of transistors. As a consequence, Computer Architecture has become extremely parallel at all levels. It has been preferred to have several simpler processing elements than fewer more complex and powerful ones. Two main challenges in the algorithms implemented on these modern manycore architectures have arisen: (1) Shared resources have become the norm, ranging from the memory hierarchy and the interconnections between processing elements and memory to arithmetic blocks such as double floating point units, different mechanism at software and hardware levels are used for the arbitration of these shared resources and need to be considered on the scheduling and orchestration of tasks. (2) In order to take advantage of the increasing amount of parallelism available, the number of tasks has increased and tasks have become finer, imposing new challenges for a light and balanced scheduling subject to resource and energy constraints.

The research proposed in this thesis will provide an analysis of these new scenarios, proposing new methodologies and solutions that leverage these new challenges in order to increase the performance and energy efficiency of modern many-core architectures. During the pursue of these objectives, this research intends to answer the following question:

- 1. Which is the impact of low-level compiler transformations such as tiling and percolation to effectively produce high performance code for many-core architectures?

- 2. What are the tradeoffs of static and dynamic scheduling techniques to efficiently schedule fine grain tasks with hundreds of threads sharing multiple resources under different conditions in a single chip?

- 3. Which hardware architecture features can contribute to better scalability and higher performance of scheduling techniques on many-core architectures on a single-chip?

- 4. How to effectively model high performance programs on many-core architectures under resource coordination conditions?

- 5. How to efficiently model energy consumption on many-cores managing tradeoffs between scalability and accuracy?

- 6. Which are feasible methodologies for designing power-aware tiling transformations on many-core architectures?

So far, this thesis establishes a clear methodology in order to answer these questions. This thesis addresses the research questions raised and support the claims and observations made through this document with several experiments.

We have shown the importance of tiling using dense matrix multiplication on the Cyclops-64 many-core architecture as an example. This technique alone is able to increase the performance from 3.16 GFLOPS to 30.42 GFLOPS. This performance was further improved using Instruction Scheduling and other Architecture specific optimizations reaching 44.12 GFLOPS. Later, with the use of Percolation, the new performance was 58.23 GFLOPS. We have also shown how Dynamic Scheduling can overcome a highly balanced Static Scheduling on a Matrix Multiplication. For this case, we were able to increase the performance from 58.23 GFLOPS to 70.87 GFLOPS on SRAM and from 38.73 GFLOPS to 56.26 GFLOPS on DRAM using Dynamic Percolation. These results are by far greater than any other previous published result for this architecture and it approaches the 80 GFLOPS of theoretical peak performance.

We demonstrated how Dynamic Scheduling can overcome Static Scheduling with regard to performance with other two additional applications. First, the tradeoffs of Static Scheduling (SS) vs. Dynamic Scheduling (DS) are exposed using a Memory Copy microbenchmark. Under scenarios with small amount of Hardware threads (e.g. less than 48), SS overcome DS because SS is able to produce a balanced workload with minimum overhead. However, increasing the number Thread Units makes SS schedule highly unbalanced, loosing performance. DS is a feasible solution to manage these complex scenarios and produces balanced workloads under more than a hundred Thread Units with light overhead that allows doubling the performance in some cases. Second, Sparse Vector Matrix Multiplication (SpVMM) was used to show the tradeoffs of SS vs DS under heterogeneity of task controlling the variance of the sparsity distribution for the matrix. In addition, we explained how the advantages of DS are further improved by a low-overhead implementation using mechanisms provided by the architecture, particularly *in-memory* atomic operations, diminishing the overall overhead of DS. As a result, DS can remain efficient for finer task granularities.

We have demonstrated a technique to model the performance of parallel applications on many-core architectures with resource coordination conditions. Our approach, based on timed Petri nets, results in algorithm specific models that allow us to account for the resource constraints of the system and the needs of the algorithm itself. With our approach, we were able to model the performance of a dense matrix multiplication algorithm and a finite difference time-domain (FDTD) solution in 1D and 2D with a very high degree of accuracy, an average error of 4.4% with respect to the actual performance of the algorithms. Finally, we demonstrated how to use our approach to performance modeling to investigate, develop, and tune algorithms for modern manycore architectures, we compared two different tiling strategies for the FDTD kernel and we tested two different algorithms for LU Factorization.

We also proposed a general methodology for designing tiling techniques for energy efficient applications. The methodology proposed is based on an optimization problem that produces optimal tiling and sequence of traversing tiles minimizing the energy consumed and parametrized by the sizes of each level in the memory hierarchy. We also showed two different techniques for solving the optimization problem for two different applications: Matrix Multiplication (MM) and Finite Difference Time Domain (FDTD). Our experimental evaluation shows that the techniques proposed reduce the total energy consumption effectively, decreasing the static and dynamic component. The average energy saving for MM is 61.21%, this energy saving is 81.26% for FDTD compared with the naive tiling.

We studied and implemented several optimizations to target energy efficiency on many-core architectures with software managed memory hierarchies using LU factorization as a case of study. Starting with an implementation optimized for High Performance. We analyzed the impact of these optimizations on the Static Energy  $E_s$ , Dynamic Energy  $E_d$ , Total Energy  $E_T$  and Power Efficiency using the energy model previously developed. We designed and applied further optimizations strategies at the instruction-level and task-level to directly target the reduction of Static and Dynamic Energy and indirectly increase the Power Efficiency. We designed and implemented an energy aware tiling to decrease the Dynamic Energy. The tiling proposed minimizes the energy contribution of the most power hungry instructions. The proposed optimizations for energy efficiency increase the power efficiency of the LU factorization benchmark by 1.68X to 4.87X, depending on the problem size, with respect to a highly optimized version designed for performance. In addition, we point out examples of optimizations that scale in performance but not necessarily in power efficiency.

Finally, we showed tradeoffs between performance and energy optimizations for Many-core architectures. We explained the partial relation between performance and energy consumption through the Static Energy and execution time. We detailed some reasons that explain why energy optimization are more challenging than performance optimizations including: a) Performance optimizations just target directly the Static Energy component, with diminishing benefits for the total energy consumption. b) Some performance optimizations can affect negatively the Dynamic Energy component diminishing even more the benefits for total energy; and c) Latency can be hidden but energy cannot be; while multiple performance optimizations target a better use of resources by reordering instructions, computations or tasks in order to hide latency, the amount of work performed and the energy associated keep the same. All these reasons motivate a deeper look at strategies that optimize Dynamic Energy such as the Power Aware Tiling. Last, we showed how to exploit tradeoffs between performance and energy using a parametric power aware tiling on a parallel matrix multiplication. We reached 42% energy saving allowing a 10% decrease in performance using a rectangular tiling instead of an square tiling.

#### Chapter 1

#### INTRODUCTION

The first stage of the evolution in microprocessors were dominated by an uninterrupted increase in processor frequency, transistor count and processor functionality. As a consequence, programmers had needed minimum effort to increase the performance of their programs because all the new improvements in hardware reflected on automatic gains in performance. Unfortunately, these automatic gains can not be sustained anymore because limitations in frequency and single processor functionality have reach their limits.

These limitations are better known as *walls*. They are related to physical constrains such as the *frequency wall* and the *power wall* or architectural constrains such as the *memory wall* and the *ILP wall*

#### 1.1 Frequency Wall

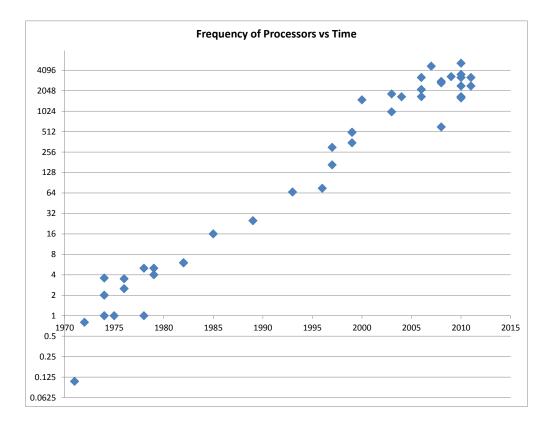

Frequency of processors had followed and exponential increase from early 70's to approximately 2004 when it reached a threshold around 4GHz as can be seen in Figure 1.1. Unfortunately, several factors stop the frequency increase and motivate to decrease the frequency on future generations of processors. The main factor is the relation between frequency and dynamic power given by Eq. 1.1

$$P_d = f \cdot C \cdot V_{DD}^2 \tag{1.1}$$

The increase in density of transistors for a single chip and the increasing in frequency has pushed silicon to is thermal limit before melting. In addition, the electromagnetic side effects produced by higher frequencies introduce additional difficulties in the hardware design process.

Figure 1.1: Processor Frequency over time

#### 1.2 Power Wall

Power consumption in processors grew rapidly thanks to the increasing frequency of processors and complexity of single processor cores. Heat generated by processor makes necessary the use of passive heat sinks but later cooling systems where required in order to keep the silicon at safe temperatures. Unfortunately it produces additional increases in the power budget of a single-processor system. At the end, power density is too high for a cost-effective cooling [1]

Unfortunately, this increase in power is not scalable in the supercomputer field. Electrical energy cost and the infrastructure required to provide the electrical power to modern supercomputers make economically and physically unfeasible a continuous increase on power consumption. Power budget is a new variable on modern architectures that limits not only the frequency of operation but also the architecture itself.

#### 1.3 Instruction Level Parallelism (ILP) Wall

The increased capabilities of processors have played a significant role in the advances of Computer Architecture. The main objective of Instruction Level Parallelism (ILP) is to increase the number of Instructions completed Per Cycle (IPC) or decreasing its reciprocal, the average cycles to complete an instruction - Clocks Per Instruction (CPI). The development of Vector Processing highly benefit the ILP, favoring specially the field of High Performance Computing (HPC). However, it failed to penetrate the processor market at large due to their high cost at that time.

Starting in the late 60's, the development of new features provided greatest impact in the consumer market, increasing the IPC of single processor architectures at that time. These new features include Scoreboarding [2] that allows out of order completion of instructions, the Tomasulo's algorithm [3] that enables multiple instructions to be issued at the same time and the Reorder Buffer that allowed speculative execution, among others.

However, the complexity of processors with higher IPC increases quadratically with the number of simultaneous instructions supported [4]. For example, the Intel Pentium II achieved only a 1.44X speedup over its predecessor, the Intel Pentium, which uses half the number of transistors. In addition, if hardware is able to execute multiple instructions at the same time, programs are not able to provide sufficient independent instructions. Despite the efforts from compiler and computer architecture sides, the maximum IPC has been constant in around 4 instructions per cycle during the past few years. This is due to the complexity in processor architecture and the data and control dependencies in programs.

#### 1.4 Memory Wall

The increasing number of transistors per die area has allowed to include additional function units in processors and also larger memories. Today, memory sizes continue increasing, they can store billions of bits, but their speed has not increased as rapidly as the speed of processor chips. This has created a gap between the speed of processors and the speed of memories.

Several techniques has been used to leverage this disparity between processors and memories. They include additional levels of automatic cache that take advantage of locality or prefetching units and context switches that try to hide the latency of data movement. However, the memory wall is still challenging and several programs, including HPC ones, are memory bounded. The limitation is the memory bandwidth required to keep busy the computing units.

#### 1.5 Moore's Law

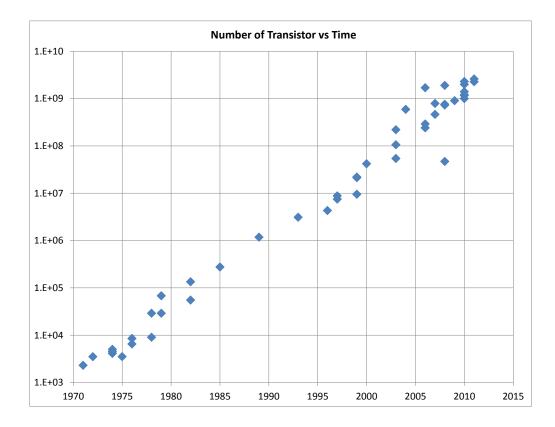

Despite the limitations reached on modern computer architecture for single processors, the increase in transistor count per die following Moore's law is still valid [5]. The number of transistors per die area continue doubling every 18 months following the observation of Gordon E. Moore in his 1965 paper. Figure 1.2 shows how the number of transistors per die grows exponentially, even after frequency of single processors stop to increase.

Now, in order to overcome and leverage the effects of the Walls that have been explained, the extra transistors are used to include additional processing elements, bringing a parallel computing revolution.

#### 1.6 Parallel Computing Era

Parallel Computing is not new. Countless efforts to design and build parallel machines have been attempted at several points in the past.

In 1962, Borroughs Corporation introduced the D825, a computer with 4 processors and 16 memory modules accessed through a crossbar switch. Also in 1969, Honeywell introduced a symmetric multiprocessor system with 8 processors in parallel: the first Multics system.

Figure 1.2: Number of Transistors over time

Single Instruction Multiple Data parallel computers started with the ILLIAC IV in 1964, from University of Illinois. It was able to work with 256 processors and large data sets, taking advantage of vector processing. Later, Seymour Cray - chief engineer and co-founder of Cray Research - was the architect of the Cray-1 in 1976. They were followed by the Cray X-MP and Cray Y-MP in 1982 and 1988.

Dataflow has lead another one of the first efforts, proposed a fully parallel machine using the concept of Dataflow Procedure Language [6]. Later the architecture of a highly concurrent multiprocessor which runs programs expressed in data flow notation was proposed [7]. It was followed by other related efforts such as the U-interpreter in 1982 [8], and the Manchester Computer in 1986 [9].

These early successful initiatives started in the academia but failed to penetrated

the market. The trend of serial processors and serial programming models continued for several years with a continuous and stable increase in performance until the walls described in Sections 1.1, 1.2, 1.3 and 1.4 forced to rethink about Parallel Computer Architecture. The increase in performance comes from the use of several processing elements inside a single chip. This new paradigm on the common scenarios found in many-core architectures (e.g. large number and heterogeneity of resources) requires the study and development of new techniques that seek finer granularity and a greater interplay in the sharing of resources. As a result, several elements of computer systems and algorithm design need to be re-evaluated under these new scenarios, it includes runtime systems, scheduling schemes and compiler transformations.

#### 1.7 Document Organization

The rest of this thesis is organized as follows: Chapter 2 presents an overview of Dataflow. Chapter 3 introduces the Problem Formulation and Research Questions developed along this thesis. Chapter 4 explains the IBM Cyclops-64 (C64) many-core architecture used in this work. Chapter 5 presents Low-level compiler transformations for high performance on many-cores. Chapter 6 discusses Dynamic Techniques for fine-grain, highly parallel programs. Chapter 7 explains a method to model the performance of Many-core Architectures under Dynamic Scheduling and Resource Constraints. Chapter 8 proposes an scalable Energy Consumption Model for many-cores and Power Aware Tiling Transformations. Chapter 9 discusses Energy Optimizations in the context of Many-core Architectures. Chapter 10 explains some trade offs between Performance and Energy optimizations. Chapter 11 outlines the related work and extensions of this research. Finally, Chapter 12 presents the summary and conclusions of this thesis.

## Chapter 2 AN OVERVIEW OF DATAFLOW

The dataflow program execution model, also know as dataflow for short, is an alternative to the traditional von Neumann execution model. Dataflow relies on a graph representation of the program and its advantages are the complements of stored-program in von Neumann's model. During the las forty or so years since it was proposed, this model of computation has been used and developed in several areas of computing research ranging from programming languages to processor design, including applications to signal processing and reconfigurable computing. This chapter summarizes the current state-of-the-art in the evolution of dataflow, focusing on multithreaded computing.

Dataflow is a very simple but powerful model for parallel computation. Dataflow programming and architectures do not have the notion of program counter or control flow such as a conventional sequential computer. In a dataflow model, computation is described in terms of local events that correspond to the firing of an actor. An actor is a single instruction or a sequence of instructions, the dataflow model does not impose a limitation on the size or the complexity of an actor. An actor can fire when all the inputs are available, in consequence many actors can fire at the same time, representing asynchronous concurrent computation events [10].

The dataflow model of execution has its roots in the work of several researchers [11, 12, 13, 6]. In the early 70's, dataflow computer architecture emerged with the use of dataflow graphs in programs to represent and exploit parallelism in them.

Dataflow allows distributed scheduling (each actor can decide "on its own" whether it is ready to fire or not), rather than relying upon a central controller to do so. In addition, the model of execution do not require a central memory system for the data elements. They are passed directly from the instructions that produce them to those that consume them.

#### 2.1 The Static Model

Static dataflow machines share the property that in the dataflow graphs on which they are based, an arc can only hold one token. As a consequence, if there is a section of a program which is executed repeatedly (e.g., a loop body or a subroutine), the corresponding section of the dataflow graph cannot allow simultaneous execution of more than one instance of that code. There are two ways to solve this problem:

- 1. Pipeline the execution of the graph: Pipelining the graph for maximal parallelism requires that the graph have a structure analogous to pipelined processors. The graph must be organized neatly into stages, with no internal cycles, and all paths through the graph must have the same length. Thus, shorter paths need to be filled with identity actors that simply pass tokens along [14]

- 2. Replicate the graph: Replicating the graph works well when the number of iterations can be determined at compile time, as in regular numerical applications, but not when iteration counts are determined dynamically, e.g., irregular loops or binary recursion.

An architecture to execute dataflow graphs was proposed by Dennis and Misunas at MIT [11]. Their idea was to convert a dataflow graph into an essentially isomorphic structure which would be more amenable to execution on real hardware. On dataflow graphs, the arguments of actors flow on the arcs as tokens, this type of machines similar to the Dennis-Misunas architecture are known as *argument-flow machines*. Other argument-flow machines were later proposed [13, 15]

A shortcoming of the argument-flow implementations is the need for extra storage for copying operands. As an alternative, The *argument-fetch machines* were proposed to address this issue. In argument-fetch machines, data values are not attached to a specific actor, but can be stored anywhere in the Operand Memory. This means that instructions must contain references to those locations. Data no longer flows from one actor to another; only signals flow. The program in an argument-fetch machine looks much less like a dataflow graph, though it is functionally equivalent if constructed properly.

#### 2.2 The Unraveling Interpreter

While the static interpreter allows only one instance of an instruction at a time, the U-interpreter proposed by Arvind [12] allows an indefinite number of instances of a specific instruction to exist, as a loop unravels. This is done by adding iteration tags to each data element and allowing execution of an instruction when its input operands have arrived and they all carry identical iteration tags. Among other parameters, a tag contains the iteration to which the data token belongs (other fields are used for nested loops and recursive calls). The iteration field of the tag does not change within the body of a loop but may be modified by special operators when a data element is transferred from one iteration to another.

This interpretation model is quite dynamic because it exposes, at runtime, all the parallelism that is inherent to the program graph being executed. However, this comes at a price. First, an undesirable situation could develop as the program unravels, It will happen when some parts of the program "run ahead," while others are bogged down since there is no central control. This could result in some local resources being overwhelmed. In a related issue, the size of the tag could grow indefinitely in a situation not unlike. However, again because of the lack of control, there would be no way to keep this in check.

Despite the interesting possibilities presented by the U-interpreter, its generality causes it to be impractical. A better understanding of the program structure and control on the granularity are required.

#### 2.3 Architecture Prototypes and Implementations

The initial research on dataflow scheduling spawned several architecture implementation projects. One of the firsts was the LAU machine [16] which relied upon a single assignment language at the high level and upon associative memories to identify ready instructions.

In another project, the Hughes Data-flow Machine (HDFM) [17] offered several interesting hybrid concepts such as a higher granularity for acknowledgment between blocks, update-in-place for large structures, as well as specialized handling for lower dimensional arrays. Simulation results were promising and emphasized the need to be "application-driven."

One of the most important projects in the area, the Monsoon Dataflow Machine [18, 19], resulted in actual machines manufactured my Motorola which were distributed to various research groups for evaluation. Monsoon was based on the Unraveling Interpreter and actually implemented a mapping from the "virtual" tag to a "physical" tag through a conversion process which entailed partitioning the code into blocks of execution. One of the guiding principles behind the design of Monsoon was the close mapping which existed between the high-level language Id (functional, single assignment) and the low-level data-flow principles of execution. Monsoon was eventually superseded by a more multi-threaded version, the StarT [20].

At that time, the technology did not always allowed a large amount of parallelism, also the level of granularity used on the partition, allocation and scheduling did not take into account well-known program constructs, causing an increasing sequential overhead. Finally, the increasing performance of single processor machines, through frequency scaling, decreased the interest on this new type of parallel machines.

#### 2.4 Dataflow and Multithreaded Execution

Challenges for suitable multithreaded computer architecture in general purpose parallel computers are the subject of intensive debate. They depend heavily on the program execution model selected, affecting the programming model, the organization of the system and the development and support of applications implemented in the architecture (e.g. compiler, runtime system and tools) [21, 22]. In this context, a program execution model defines a basic low-level layer of programming abstraction of the underlaying system architecture upon which the architecture model, programming model, compilation strategy, runtime system, and other software components are developed. It serves as an interface between the architecture and the software [10]. Program execution model is in a broader (or higher) level than instruction set architecture (ISA) specification. An ISA usually provides a description of an instruction set for a particular machine that involves specific details of instructions such as instruction encoding and the organization of the machine registers set. In the context of this work, a program execution model for multithreaded machines includes the following aspects: the thread model, the memory model and the synchronization [10].

Traditionally, the dataflow model and von Newmann serial control flow model are viewed as two execution models on opposite sites used to design a spectrum of architecture models. However, they are not orthogonal: Based on the operational model of a pure dataflow graph, it can be extended to support von Newmann program execution style. A region of actors in a dataflow graph can be grouped as a thread and executed sequentially under a private program counter; at the same time, activation and syncronization of threads can be data-driven. This hybrid model is flexible and it can combine dataflow and control-flow evaluation, exposing parallelism at a desired level.

As an example, the McGill Dataflow Architecture Model (MDAM) [23, 24] has been proposed based on the argument-fetching principle. The architecture departs from a direct implementation of dataflow graphs by having instructions fetch data from memory or registers instead of having instructions deposit operands (tokens) in "operand receivers" of successor instructions. The completion of an instruction will post an event (called a signal) to inform instructions that depend on the results of the instruction. This implements a modified model of dataflow computation called dataflow signal graphs [25]. The ideas of Iannucci, inspired by his experience on dynamic dataflow architectures, combined dataflow models with sequential thread execution on a hybrid computation model that later evolved into a multithreaded architecture at IBM [26, 27]. This architecture includes features such as cache memory with synchronization controls, prioritized processor ready queues and features for efficient process migration to facilitate load balancing.

Multithreaded execution models with dataflow origin provide support for finegrain threads at two levels. For example, under the EARTH model [28, 29, 30], the first level of threads is called threaded function invocation: parallel function invocation forks a thread to execute the function in parallel. Note that the caller continues its own execution without waiting for the return of the forked threaded function. At a lower (finer) level, the body of a threaded function can be further partitioned (by a user or a compiler) into fibers: a collection of operations that can be forked as a separate thread. In this way, it is possible to define a thread model combining the advantages from both the static and dynamic dataflow models: the thread function invocation provides full generality as in the dynamic data flow model, while the finer level of threads maintains the simplicity of the static dataflow through software pipelining.

Recently, another hierarchical multithreading model featuring a novel eventdriven, fine-grain, multithreading model has been proposed. The Codelet Execution Model is a new model centered on the concepts and semantics of codelets [31, 32]. The execution model is based on the EARTH model [33] and has been extended by Dennis's Fresh Breeze Tree-Based Memory Model [34] and also well explored by the ongoing DOE X-Stack execution model [31]. The codelet-based model has good features for exascale systems design. Even though codelets have a higher granularity than individual instructions, their granularity remains finer than that used by the execution models of the commercial CPUs. The Codelet Execution Model is a hybrid model that incorporates the advantages of macro-dataflow[26, 23, 10] and the Von Neumann model. The Codelet Execution Model can be used to describe programs in massively parallel systems, including hierarchical or heterogeneous systems. The Codelet Execution Model extends traditional macro-dataflow models in the way shared system resources are managed. The management of such resources is accomplished through events created by threads. As in macro-dataflow, computation is done through units of small serial code known as *codelets*, and execution is based solely on the availability of the data required. Codelets are executed based on required events. An event can consist of the availability of (shared) resources including data, processing elements, bandwidth, energy, etc. Codelets are tagged with resource requirements and linked together by data dependencies to form a graph (analogous to a dataflow graph [35]). This graph is further partitioned into asynchronous procedures which are invoked in a controlled flow manner. Moreover, the definition of events and the explicit expression and inclusion of system resources in the parallel execution model makes the Codelet Execution Model a promising model capable of addressing the power issues faced by future large-scale computer systems. Works that use the codelet model include ETI's SWift Adaptive Runtime Machine (SWARM) [36] and TIDeFlow [37, 38, 39].

## Chapter 3 PROBLEM FORMULATION

The new many-core era motivated by the recent efforts to build peta-scale and exa-scale machines have brought several challenges for exploiting the parallelism on new many-core architectures with hundreds, or even thousands, of independent processing elements. The scenario inside these chips is different to previous multi-core processors, some of the new characteristics are:

- Increasing amount of shared resources.

- Heterogeneity of resources.

- Diversity in coordination and arbitration mechanisms for shared resources.

- Constraints in energy consumption.

This new environment requires new techniques that seek finer granularity and a greater interplay in the sharing of resources. These work re-evaluate several elements of computer systems and algorithm design under these new scenarios, it includes runtime systems, scheduling schemes and compiler transformations.

Moore's law is still valid, the number of transistor in a single chip doubles every 18 months approximately, but single processor architectures are not able to take advantage of the increasing amount of transistors. Today, Computer Architecture has become extremely parallel at all levels. The many-core era has arisen: A large number of simple processing elements are preferred over few very complex but powerful processors.

This new era brings two main challenges in the algorithms implemented on these modern many-core architectures:

- 1. Shared resources have become the norm, ranging from the memory hierarchy and the interconnections between processing elements and memory to arithmetic blocks such as double floating point units, different mechanism at software and hardware levels are used for the arbitration of these shared resources and need to be consider on the scheduling and orchestration of tasks.

- 2. In order to take advantage of the increasing amount of parallelism available, the number of tasks has increased and tasks have become finer, imposing new challenges for a light and balanced scheduling subject to resource and energy constraints.

The research proposed here will provide an analysis of these new scenarios, proposing new methodologies and solutions that leverage these new challenges in order to increase the performance and energy efficiency of modern many-core architectures. During the pursue of these objectives, this research intends to answer the following question:

- 1. Which is the impact of low-level compiler transformations such as tiling and percolation to effectively produce high performance code for many-core architectures?

- 2. What are the trade-offs of static and dynamic scheduling techniques to efficiently schedule fine grain tasks with hundreds of threads sharing multiple resources under different conditions in a single chip?

- 3. Which hardware architecture features can contribute to better scalability and higher performance of scheduling techniques on many-core architectures on a single-chip?

- 4. How to effectively model high performance programs on many-core architectures under resource coordination conditions?

- 5. How to efficiently model energy consumption on many-cores managing trade offs between scalability and accuracy?

- 6. Which are feasible methodologies for designing power-aware tiling transformations on many-core architectures?

So far, this thesis establish a clear methodology, propose solutions and provide evidence in order to answer these questions.

# Chapter 4

# AN INNOVATIVE MANY-CORE ARCHITECTURE

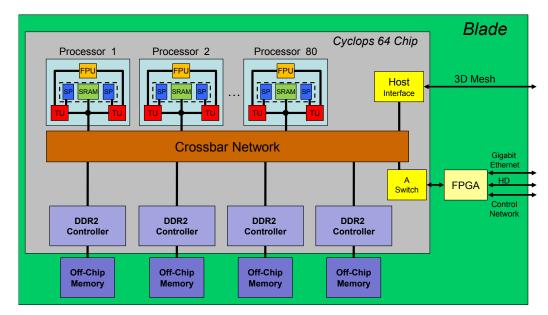

Cyclops-64 (C64) is an innovative architecture developed by IBM, designed to serve as a dedicated petaflop computing engine for running high performance applications. A C64 chip is an 80-processor many-core-on-a-chip design, as can be seen in Figure 4.1. Each processor is equipped with two thread units (TUs), one 64-bit floating point unit (FP) and two SRAM memory banks of 30kB each. It can issue one double precision floating point "Multiply and Add" instruction per cycle, for a total performance of 80 GFLOPS per chip when running at 500MHz.

Figure 4.1: C64 Chip Architecture

A 96-port crossbar network with a bandwidth of 4GB/s per port connects all TUs and SRAM banks. The total crossbar network bandwidth of 384GB/s supports

Figure 4.2: Memory Hierarchy of C64

both the intra-chip communication, as well as the six routing ports that connect each C64 chip to its neighbours [40]. The complete C64 system is built out of tens of thousands of C64 processing nodes arranged in a 3-D mesh topology. Each processing node consists of a C64 chip, external DRAM, and a small amount of external interface logic.

### 4.1 Memory Hierarchy

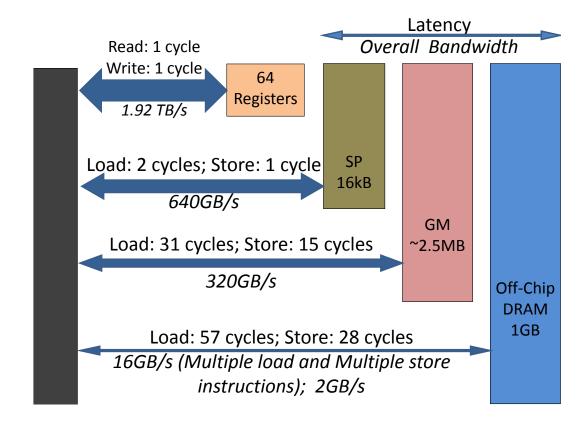

A C64 chip has an explicit three-level memory hierarchy (scratchpad memory, on-chip SRAM, off-chip DRAM), 16 instruction caches of 32kB each (not shown in the figure) and no data cache. The scratchpad memory (SP) is a configured portion of each on-chip SRAM bank which can be accessed with very low latency by the TU it belongs to. The remaining sections of all on-chip SRAM banks consist the on-chip global memory (GM), which is uniformly addressable from all TUs. As a summary, Figure 4.2 reflects the current size, latency (when there is no contention) and bandwidth of each level of the memory hierarchy.

Execution on a C64 chip is non-preemptive and there is no hardware virtual memory manager. The former means that the C64 micro-kernel will not interrupt the execution of a user application unless an exception occurs. The latter means the three-level memory hierarchy of the C64 chip is visible to the programmer.

All memory controllers in C64 support *in-memory* atomic operations: Each memory controller has an ALU that allows it to execute atomic operations in 3 clock cycles directly inside the memory controller (both SRAM and DRAM), without help from a thread unit.

### 4.2 Energy Consumption

Because C64 is a general purpose many-core architecture it has not been designed for energy efficiency and it does not have special features for saving power. For example, it is not possible to turn off cores not used or to slow down the clock rate of a set of cores or for the whole chip.

Despite the fact that the C64 Instruction Set Architecture (ISA) does not include any additional instructions that help reduce energy consumption we can group the instructions according to the hardware units they use and the complexity of the operation (reflected indirectly on the execution time if there is not contention). Furthermore, we can use these groups to build our energy consumption model. According with that, the taxonomy proposed for the ISA is:

- Logical Operations: And, or, etc.

- Integer Arithmetic Operations:

- Simple: Add, sub.

- Medium: Multiply.

- Floating Point Operations:

- Simple: Add, sub.

- Medium: Multiply, multiply and add.

- Memory Operations:

- On Registers: Move, load immediate.

- On SPM: load, store.

- On SRAM: load, store.

- On DRAM: load, store.

Some instructions not mentioned here. For example, branches can be included in the logical operations category, given the hardware resources and amount of work they require.

#### Chapter 5

# STATIC OPTIMIZATIONS IN THE CONTEXT OF MANY-CORE ARCHITECTURES

Traditional parallel programming methodologies for improving performance assume cache-based parallel systems. They exploit temporal locality making use of cache tiling techniques with tile size selection and padding [41, 42]. However, the data location and replacement in the cache is controlled by hardware making fine control of these parameters difficult. In addition, power consumption and chip die area constraints make increasing on-chip cache an untenable solution to the memory wall problem [43, 44].

As a result, new architectures like the IBM Cyclops-64 (C64) belong to a new set of many-core-on-a-chip systems with a software managed memory hierarchy. These new kinds of architectures hand the management of the memory hierarchy to the programmer and save the die area of hardware cache controllers and over-sized caches. Although this might complicate programming at their current stage, these systems provide more flexibility and opportunities to improve performance. Following this path, new alternatives for classical algorithmic problems, such as Dense Matrix Multiplication (MM), LU Factorization (LU) and Fast Fourier Transform (FFT) have been studied under these new many-core architectures [45, 46, 47]. The investigation of these new opportunities leads to two main conclusions: (1) The optimizations for improving performance on cache-based parallel system are not necessarily feasible or convenient on software managed memory hierarchy systems. (2) Memory access patterns reached by appropriate tiling substantially increase the performance of applications.

Based on these observations we can conclude that new programming and compiling methodologies are required to fully exploit the potential of these new classes of architectures. We believe that a good starting point for developing such methodologies are classical algorithms with known memory access and computation patterns. These applications provide realistic scenarios and have been studied thoroughly under cache-based parallel systems.

Following this idea, we present a general methodology that provides a mapping of applications to software managed memory hierarchies, using MM on C64 as a case of study. MM was chosen because it is simple to understand and analyze, but computationally and memory intensive. For the basic algorithm, the arithmetic complexity and the number of memory operations in multiplications of two matrices of sizes  $m \times m$ are  $O(m^3)$ .

The methodology presented in this thesis is composed of three strategies that result in a substantial increase in performance, by optimizing different aspects of the algorithm. The first one is a balanced distribution of work among threads. Providing the same amount of work to each thread guarantees minimization of the idle time of processing units waiting for others to finish. If a perfect distribution is not feasible, a mechanism to minimize the differences is proposed. The second strategy is an optimal register tiling and sequence of traversing tiles. Our register tiling and implementation of the sequence of traversing tiles are designed to maximize the reuse of data in registers and minimize the number of memory accesses to slower levels, avoiding unnecessary stalls in the processing units while waiting for data. The last strategy involves more specific characteristics of C64. The use of special instructions, optimized instruction scheduling and other techniques further boost the performance reached by the previous two strategies. The impact on performance can change according to the particular characteristics of the many-core processor used.

The experimental evaluation was performed using a real C64 chip. After the implementation of the three strategies proposed, the performance reached by the C64 chip is 44.12 GFLOPS, which corresponds to 55.2% of the peak performance.

### 5.1 Classic Matrix Multiplication Algorithms

MM algorithms have been studied extensively. These studies focused mainly on two areas: (1) Algorithms that decreases the naïve complexity of  $O(m^3)$ . (2) Implementations that take advantage of advanced features of computer architectures to achieve higher performance. This study is oriented towards the second area.

In the first area, more efficient algorithms are developed. Strassen's algorithm [48] is based on the multiplication of two 2 × 2 matrices with 7 multiplications, instead of 8 that are required in the straightforward algorithm. The recursive application of this fact leads to a complexity of  $O(m^{\log 7})$  [49]. Disadvantages, such as numerical instability and memory space required for sub-matrices in the recursion, have been discussed extensively [50, 51]. The current best lower bound is  $O(m^{2.376})$ , given by the Coppersmith–Winograd algorithm [52]. However, this algorithm is not used in practice, due to its large constant term.

The second area focuses on efficient implementations. Although initially more emphasis was given towards implementations for single processors, parallel approaches quickly emerged. A common factor among most implementations is the decomposition of the computation into blocks. Blocking algorithms not only give opportunities for better use of specific architectural features (e.g., memory hierarchy) but also are a natural way of expressing parallelism. Parallel implementations have exploited the interconnection pattern of processors, like Cannon's matrix multiply algorithm [53, 54, 55], or the reduced number of operations like Strassen's algorithm [56, 57, 58]. These implementations have explored the design space along different directions, according to the targeted parallel architecture.

The many-core architecture design space has not yet been explored in detail, but existing studies already show their potential. A performance prediction model for Cannon's algorithm has shown a huge performance potential for an architecture similar to C64 [59]. Previous research of MM on C64 showed that is possible to increase performance substantially by applying well known optimizations methods and adapting them to specific features of the chip [46]. More recent results on LU Factorization conclude that some optimizations that performs well for classical cached-based parallel system are not the best alternative for improving performance on software managed memory hierarchy systems [47].

### 5.2 Proposed Matrix Multiplication Algorithm

In this section we analyze the proposed MM algorithm and highlight our design choices. The methodology used is oriented towards exploiting the maximum benefit of features that are common across many-core architectures. Our target operation is the multiplication of dense square matrices  $A \times B = C$ , each of size  $m \times m$  using algorithms of running time  $O(m^3)$ . Throughout the design process, we will use some specific features of C64 to illustrate the advantages of the proposed algorithm over different choices used in other MM algorithms.

Our methodology alleviates three related sources identified to cause poor performance in many-core architectures: (1) Inefficient or unnecessary synchronization. (2) Unbalanced work between threads. (3) Latency due to memory operations. Relation and impact in performance of these sources are architecture dependent and modeling their interactions has been an active research topic.

In our particular case of interest, the analysis of MM is easier than other algorithms not only for the simple way it can be described but also for the existence of parallel algorithms that do not required synchronizations. It simplifies the complexity of our design process because we only need to carefully analyze in two instead of the three causes of poor performance we have identified as long as the algorithm proposed does not require synchronizations. These challenges will be analyzed in the following subsections.

## 5.2.1 Work Distribution

The first challenge in our MM algorithm is to distribute work among P processors avoiding synchronization. It is well known that each element  $c_{i,j} \in C$  can be calculated independently. Therefore, serial algorithms can be parallelized without requiring any synchronization for the computation of each element  $c_{i,j}$ , which immediately solves this requirement.

The second step is to break the  $m \times m$  matrix C into blocks such that we minimize the maximum block size pursuing optimal resource utilization and trying to avoid overloading a processor. This is optimally done by breaking the problem into blocks of  $\frac{m^2}{P}$  elements, but the blocks must be rectangular and fit into C.