## A COMPARISON BETWEEN VIRTUAL CODE MANAGEMENT TECHNIQUES

by

Joseph B. Manzano

A dissertation submitted to the Faculty of the University of Delaware in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Summer 2011

© 2011 Joseph B. Manzano All Rights Reserved

# A COMPARISON BETWEEN VIRTUAL CODE MANAGEMENT TECHNIQUES

by Joseph B. Manzano

| Approved: |                                                                |

|-----------|----------------------------------------------------------------|

| TT        | Kenneth E. Barner, Ph.D.                                       |

|           | Chair of the Department of Electrical and Computer Engineering |

|           |                                                                |

|           |                                                                |

| Approved: |                                                                |

| 11        | Babatunde Ogunnaike, Ph.D.                                     |

|           | Interim Dean of the College of Engineering                     |

|           |                                                                |

|           |                                                                |

| Approved: |                                                                |

| approved. | Charles G. Riordan, Ph.D.                                      |

|           | Vice Provost for Graduate and Professional Education           |

I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed:

Guang R. Gao, Ph.D.

Professor in charge of dissertation

I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed:

Xiaoming Li, Ph.D.

Member of dissertation committee

I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: .

Hui Fang, Ph.D.

Member of dissertation committee

I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: .

Andres Márquez, Ph.D.

Member of dissertation committee

#### ACKNOWLEDGEMENTS

As this journey ends, I would like to thank all the people that helped me during these years. First, I would like to thank my family, my sisters, Carolina and Gaby; and my parents for all their support and kind words during the years, and there have been many years. Next, I will like to thank my best friends, Juergen Ributzka, Jean Christophe Beyler and Eunjung Park for all their help and encouraging words during these years.

Next I would like to thank all the people in the CAPSL group for all the time and patience that they have had with me over the many many years that I was there. This list includes, but it is not limited to Fei Chen, Weirong Zhu, Yuan Zhang, Divya Parthasarathi, Dimitrij Krepis, Daniel Orozco, Kelly Livingston, Chen Chen, Joshua Suetterlein, Sunil Shrestha and Stephane Zuckerman. Thanks guys for several amazing years.

Finally, I want to thank my advisor, Dr Guang R. Gao and his wife, Peggy, for all their advice and guidance over the years and of course their support. As this stage is ending, I just want to let know the people in this list and many others, that you made this journey fun, exciting and worth it. Thanks from the bottom of my heart to all of you.

God bless.

## TABLE OF CONTENTS

| $egin{array}{c} egin{array}{c} egin{array}$ | ST OF FIGURES |                                                       |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------|--|--|

| <b>C</b> :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | hapte         | $\mathbf{r}$                                          |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | INT           | RODUCTION                                             |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.1           | The Power Race and Multi Core Designs                 |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | 1.1.1 The Pentium Family Line                         |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | 1.1.4 Multi Core: Intel's Core's Family of Processors |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | 1.1.5 Multi Core: Sun UltraSPARC T2                   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | 1.1.6 Multi Core: The Cray XMT                        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | 1.1.7 Many Core: The Tile64                           |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | 1.1.8 Many Core: The Cyclops-64                       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.2<br>1.3    | Problem Formulation: an Overview                      |  |  |

| <b>2</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PR            | DDUCTIVITY STUDIES                                    |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.1<br>2.2    | Atomic Sections: Overview                             |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | Overview                                              |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | 2.2.1 P3I Infrastructure and Procedures               |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | 2.2.3 P3I Results                                     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | 2.2.4 P3I Version 2                                   |  |  |

| 3 | OP  | EN OF                            | PELL: AN OVERVIEW 48                                                                                                                                                                                              |

|---|-----|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 3.1 | The C                            | dell Architecture                                                                                                                                                                                                 |

|   |     | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4 | The PowerPC Processing Element                                                                                                                                                                                    |

|   | 3.2 | Progra                           | amming Models                                                                                                                                                                                                     |

|   |     | 3.2.1                            | OpenOPELL and OpenMP                                                                                                                                                                                              |

|   |     |                                  | 3.2.1.1       Single Source Compilation       59         3.2.1.2       Simple Execution Handler       59         3.2.1.3       Software Cache       61         3.2.1.4       Overlay / Partition Manager       63 |

| 4 | PA  | RTITI                            | ON MANAGER FRAMEWORK 67                                                                                                                                                                                           |

|   | 4.1 | Toolch                           | nain Modifications                                                                                                                                                                                                |

|   |     | 4.1.1                            | Compiler Changes                                                                                                                                                                                                  |

|   |     |                                  | 4.1.1.1       Command Line Flags       69         4.1.1.2       Pragma Directives       69         4.1.1.3       Compiler Internals       71                                                                      |

|   |     | 4.1.2<br>4.1.3<br>4.1.4          | Assembler Changes                                                                                                                                                                                                 |

|   | 4.2 | Partit                           | ion Manager and Its Framework                                                                                                                                                                                     |

|   |     | 4.2.1<br>4.2.2                   | Common Terminology                                                                                                                                                                                                |

|   |     |                                  | 4.2.2.1 The Partition List       79         4.2.2.2 The Partition Stack       81         4.2.2.3 The Partition Buffer       81         4.2.2.4 The Partition Manager Kernel       81                              |

|   |                   |                         | 4.2.2.5 The Anatomy of a Partitioned Call                                                                                                                                                      |

|---|-------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                   | 4.2.3                   | Cell Implementation of the Partition Framework: Version 1 83                                                                                                                                   |

|   |                   |                         | 4.2.3.1 Partition List Structures and Variables                                                                                                                                                |

|   |                   |                         | Procedure                                                                                                                                                                                      |

|   |                   | 4.2.4                   | A Partitioned Call on CBE: Version 1                                                                                                                                                           |

| 5 | PAI               | RTITI                   | ON MANAGER ENHANCEMENTS                                                                                                                                                                        |

|   | 5.1               | The N                   | Buffer: The Lazy Reuse Approaches                                                                                                                                                              |

|   |                   | 5.1.1                   | The N Buffer Approach                                                                                                                                                                          |

|   |                   |                         | 5.1.1.1       The Partition Buffer       92         5.1.1.2       The Partition Stack       92         5.1.1.3       The Modulus Method       93         5.1.1.4       The LRU Method       94 |

|   |                   | 5.1.2                   | Cell Implementation of the Partition Framework: Version 2                                                                                                                                      |

|   | 5.2               | Partiti                 | on Graph and Other Enhancements                                                                                                                                                                |

|   |                   | 5.2.1<br>5.2.2<br>5.2.3 | Victim Cache100Prefetching100The Partition Graph100                                                                                                                                            |

|   |                   |                         | 5.2.3.1 Prefetching: Weighted Breadth First Fetch                                                                                                                                              |

|   |                   | 5.2.4                   | Dynamic Code Enclaves                                                                                                                                                                          |

| 6 | EX                | PERIN                   | MENTAL TESTBED AND RESULTS 10                                                                                                                                                                  |

|   | 6.1<br>6.2<br>6.3 | Softwa<br>Partiti       | rare Testbed                                                                                                                                                                                   |

| 7 | RE  | LATED WORK                                        |

|---|-----|---------------------------------------------------|

|   | 7.1 | A Historical Perspective                          |

|   |     | 7.1.1 The Embedded Field: Where Overlays Survived |

|   | 7.3 | Programmability for Cell B.E                      |

|   |     | NCLUSIONS                                         |

### LIST OF FIGURES

| 1.1 | 1.1a Examples of Type two[62] and 1.1b Type one architectures[30]                                                                                                                                                                                                                                                                           | 3  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

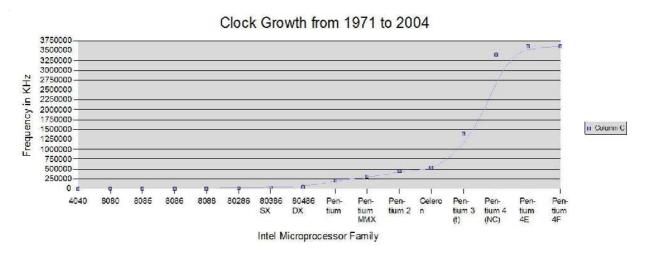

| 1.2 | Intel Processor frequency growth from 1973 to 2006                                                                                                                                                                                                                                                                                          | 6  |

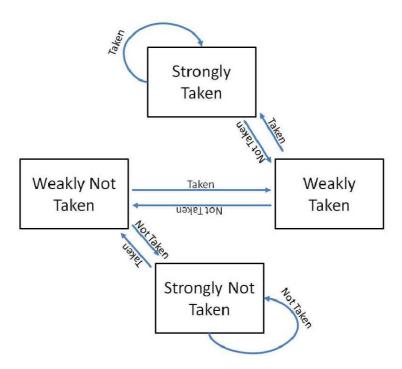

| 1.3 | The Finite Automata for a simple Two Bit Saturation Scheme. Thanks to its symmetry spurious results will not destroy the prediction schema                                                                                                                                                                                                  | 8  |

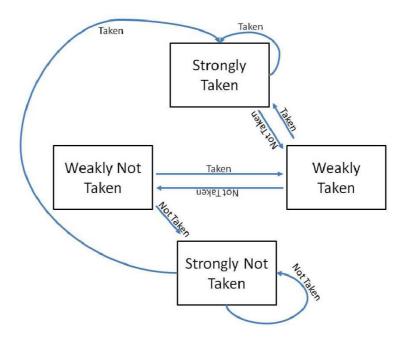

| 1.4 | The Finite Automata for the modified simple Two Bit Saturation Scheme used in the first Pentiums. Since it is not symmetric anymore the strongly taken path will jump to strongly taken after one jump which will make this path more prone to misprediction                                                                                | 8  |

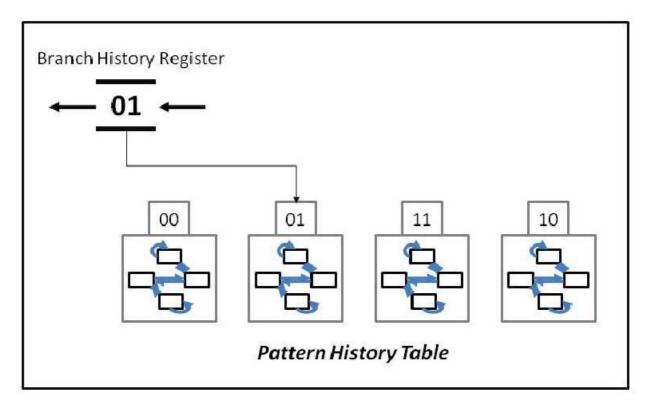

| 1.5 | Two Level Branch Predictor                                                                                                                                                                                                                                                                                                                  | 9  |

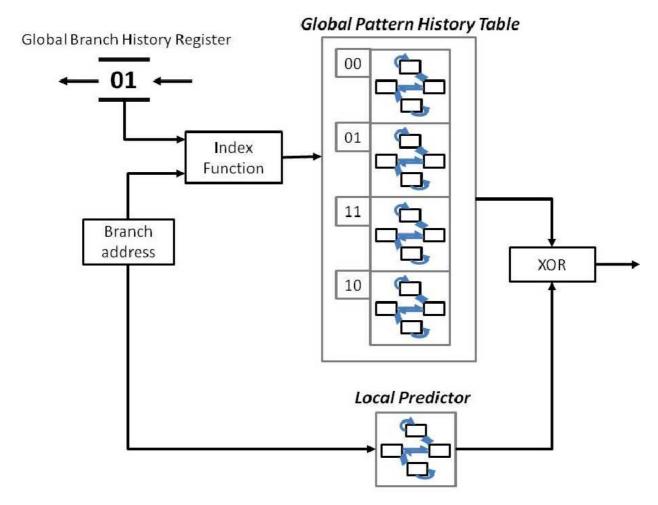

| 1.6 | The Agree Predictor                                                                                                                                                                                                                                                                                                                         | 10 |

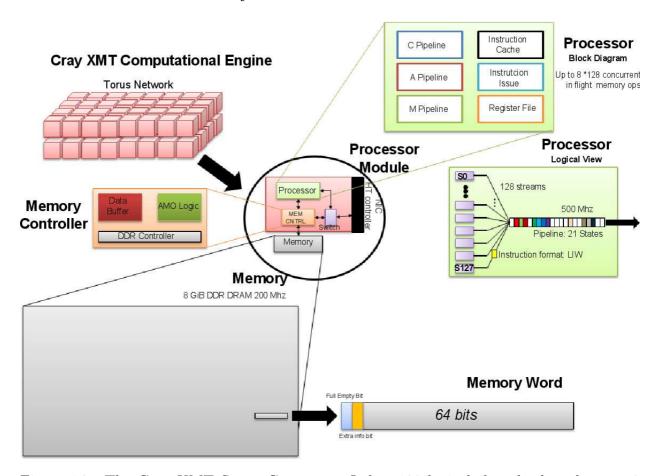

| 1.7 | The Cray XMT Super Computer. It has 128 logical threads that shares a 3 LIW pipeline. The memory subsystem sports extra bits per memory word that provides fine grained synchronization, memory monitoring, in-hardware pointer forwarding and synchronization based interrupts                                                             | 17 |

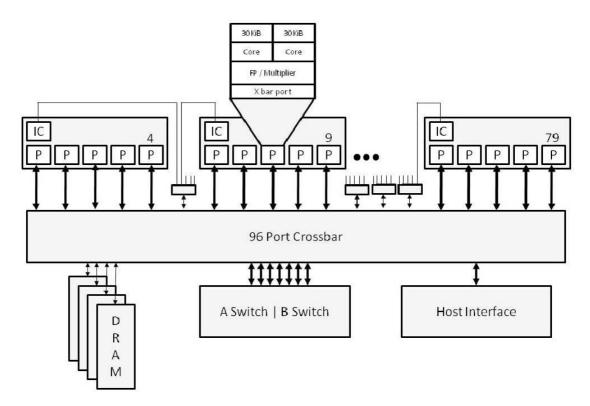

| 1.8 | A Logical diagram of the Cyclops-64 Architecture                                                                                                                                                                                                                                                                                            | 22 |

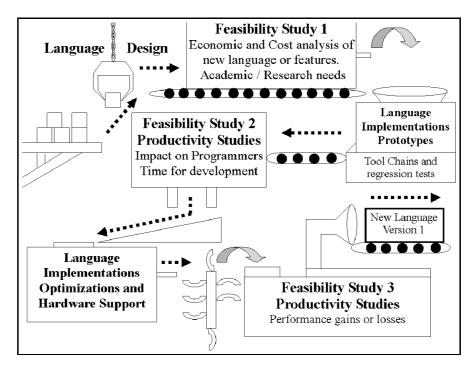

| 2.1 | A New Approach to Language Design. A new language should go through several phases in its development to ensure that it has sound syntax and semantics, it fits a specific demographic and it has a specific place in the field. Moreover, optimization to the runtime libraries should be taken into account while developing the language | 28 |

| 2.2 | Atomic Section's Syntax                                                                                                                                                                                                                                                                                                                     | 31 |

| 2.3 | Code Excerpt from Phase 0: A comparison between the lock implementation (left) and the AS implementation (right) for the unlucky banker                                                                                                                                                                                                     | 33 |

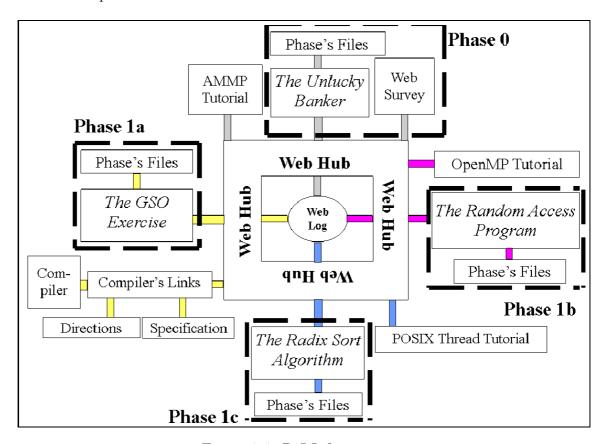

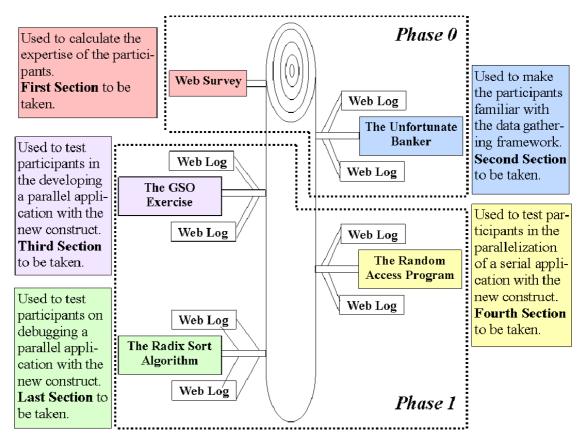

| 2.4 | P3I Infrastructure                                                                                                                                                                                                                                                                                                                          | 34 |

| 2.5  | P3I Infrastructure and Methodology                                                                                                                                                                                                               | 36 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

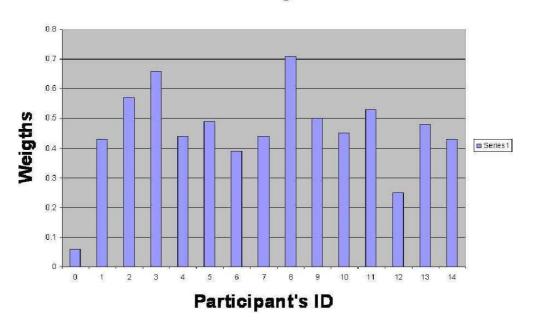

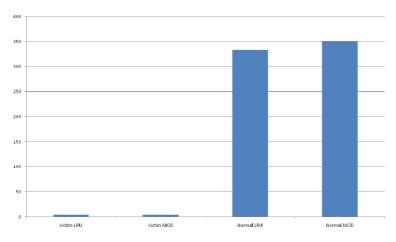

| 2.6  | Weight of each Participant                                                                                                                                                                                                                       | 38 |

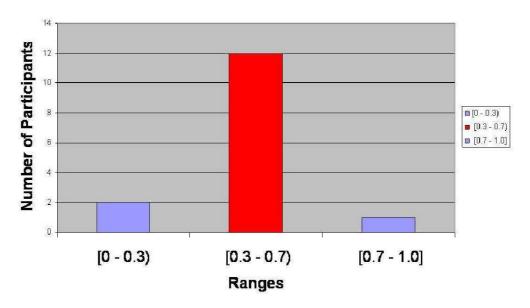

| 2.7  | Histogram of the Weights                                                                                                                                                                                                                         | 39 |

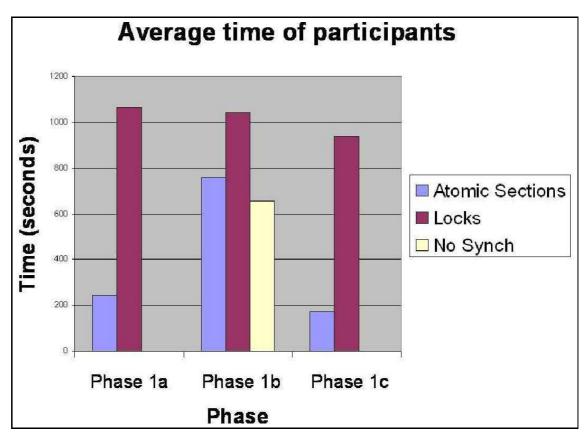

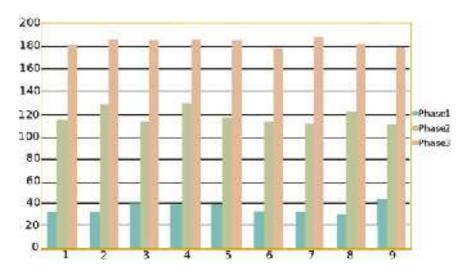

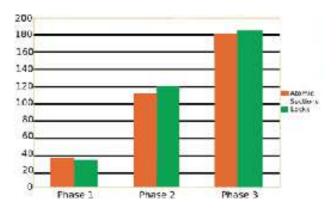

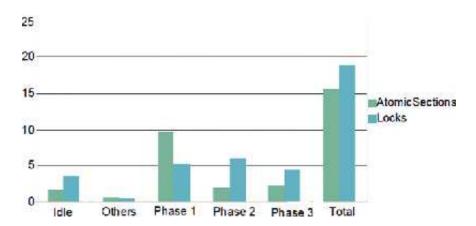

| 2.8  | Weighted Average Time Data for Each Phase. In this case, there is a clear correlation between the reduction in time to correct solution from the lock exercises and the atomic sections                                                          | 40 |

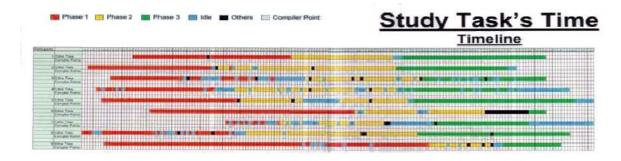

| 2.9  | Activity Timeline for each participant in the study                                                                                                                                                                                              | 41 |

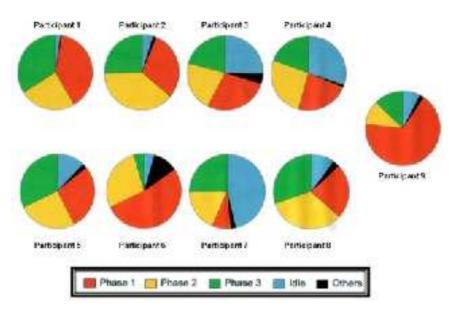

| 2.10 | The phase's percentage for each participant                                                                                                                                                                                                      | 42 |

| 2.11 | Total SLOC Average per Participant                                                                                                                                                                                                               | 42 |

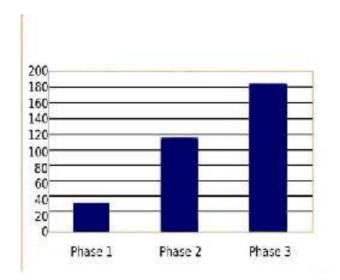

| 2.12 | Total Average for SLOC                                                                                                                                                                                                                           | 43 |

| 2.13 | Total SLOC Average per Group                                                                                                                                                                                                                     | 43 |

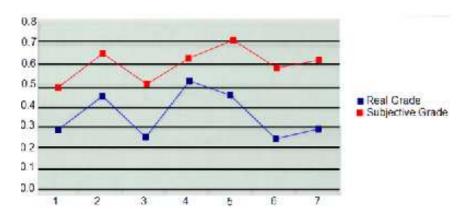

| 2.14 | A comparison between the real and subjective weights                                                                                                                                                                                             | 44 |

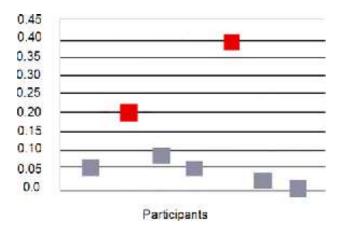

| 2.15 | An Absolute difference between the two difference types. The average difference is 0.12 and the standard deviation is 0.14 which represent very low values                                                                                       | 44 |

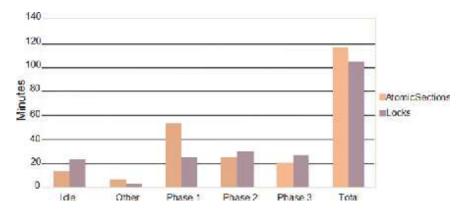

| 2.16 | The total runtimes weighted by the low expertise formula                                                                                                                                                                                         | 45 |

| 2.17 | The total runtimes weighted by the normal expertise function                                                                                                                                                                                     | 45 |

| 2.18 | The total runtimes weighted by the high expertise                                                                                                                                                                                                | 46 |

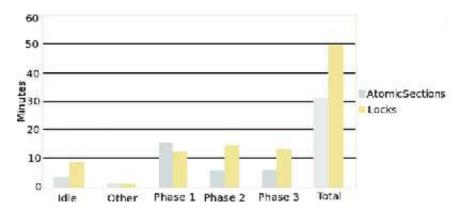

| 3.1  | Block Diagram of the Cell Broadband engine. This figure shows the block diagram of the Cell B.E. and its components (PPE and SPE). It also shows the internal structures for the SPE pipelines and a high overview graph of the interconnect bus | 49 |

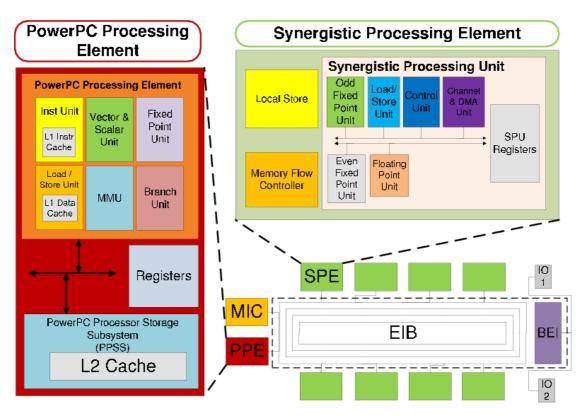

| 3.2  | Allowed and forbidden OpenMP states. Any closed and encapsulated fork-joins groups are allowed. This means that a child can never outlive its parent and the lifetimes of threads cannot overlap between regions                                 | 56 |

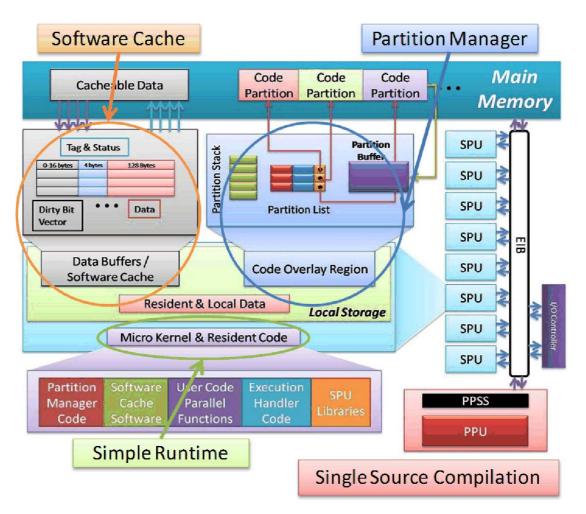

| 3.3 | High Level Overview of the Open OPELL framework. The micro kernel will take of scheduling the jobs, the single source compiler will create the binary from a single source tree, and the software cache and partition manager will take to emulate the shared memory model required by OpenMP | 58 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

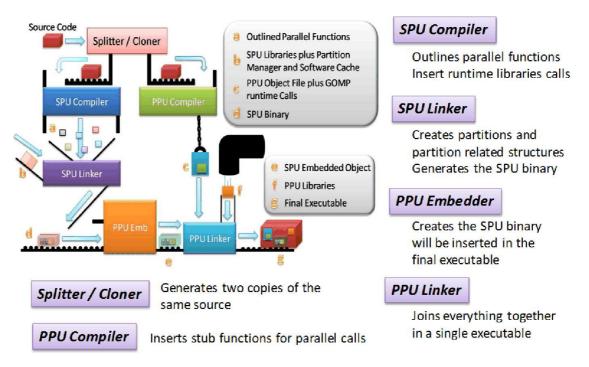

| 3.4 | A high level overview of the single source toolchain                                                                                                                                                                                                                                          | 60 |

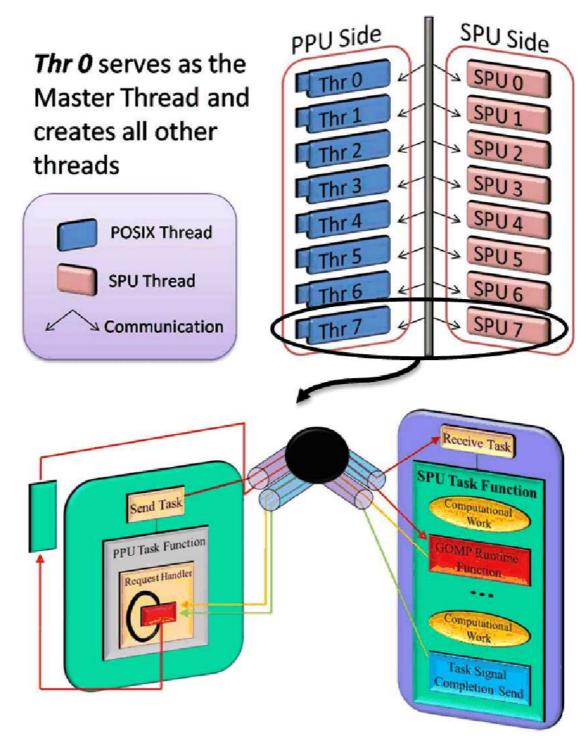

| 3.5 | Components of the Simple Execution handler. It shows the shadow threads running on the PPU side for each SPU and the communication channels and flow between them                                                                                                                             | 62 |

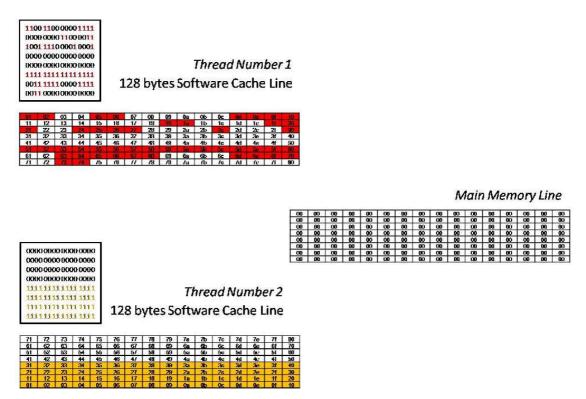

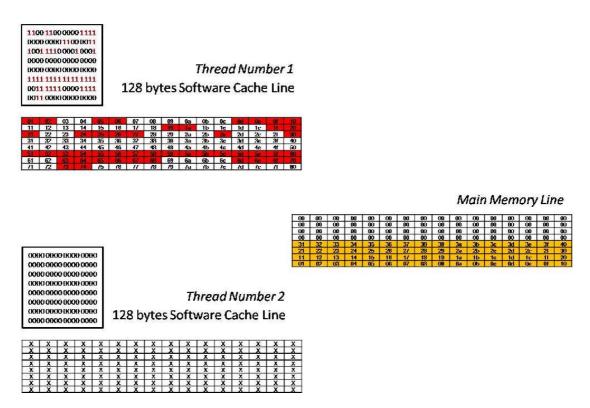

| 3.6 | Software Cache Merge Example Step 1: Before Write Back is Initialized                                                                                                                                                                                                                         | 63 |

| 3.7 | Software Cache Merge Example Step 2: Thread 2 succeed in the update. Thread 1 fails and tries again                                                                                                                                                                                           | 64 |

| 3.8 | Software Cache Merge Example Step 3: Final State of the Memory Line after Thread 1 finished                                                                                                                                                                                                   | 65 |

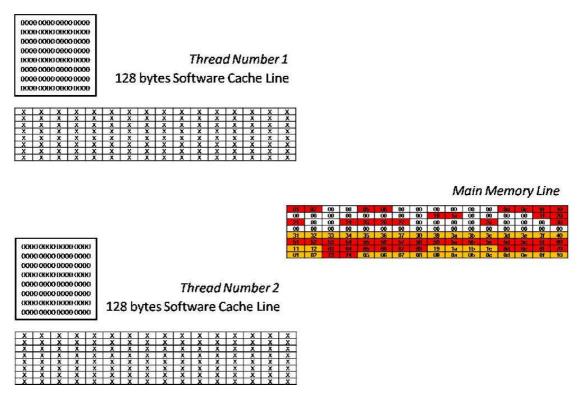

| 3.9 | A high level overview of the Software cache structure                                                                                                                                                                                                                                         | 65 |

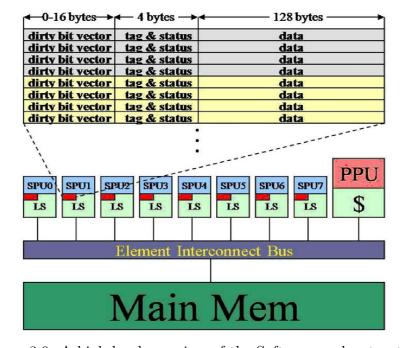

| 4.1 | Toolchain Components and their respective roles                                                                                                                                                                                                                                               | 68 |

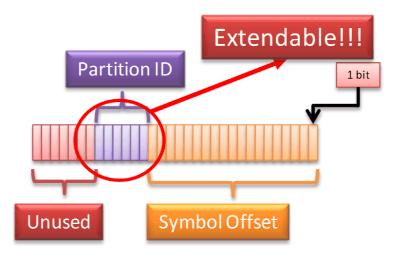

| 4.2 | The format for a Partitioned Symbol                                                                                                                                                                                                                                                           | 76 |

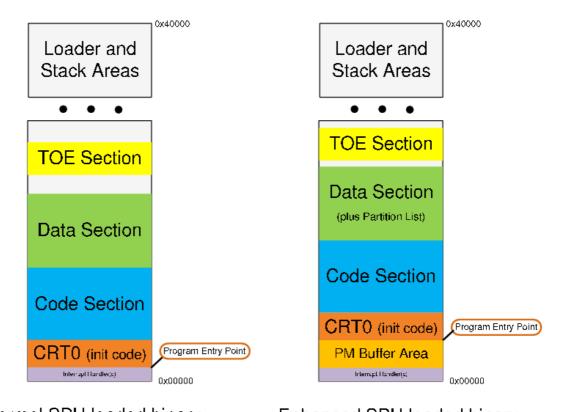

| 4.3 | The normal and enhanced binary image for the Partition Manager. The TOE segment is a special segment used for the interaction between the PPE and SPE binaries. The CRT0 represents the entire C runtime code                                                                                 | 77 |

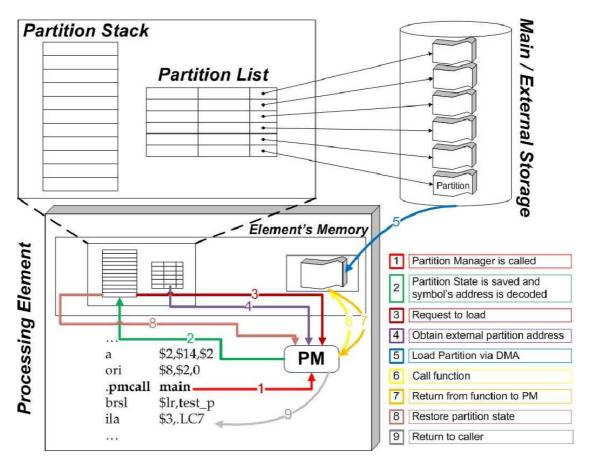

| 4.4 | A Partition Call showing all major partition manager components                                                                                                                                                                                                                               | 80 |

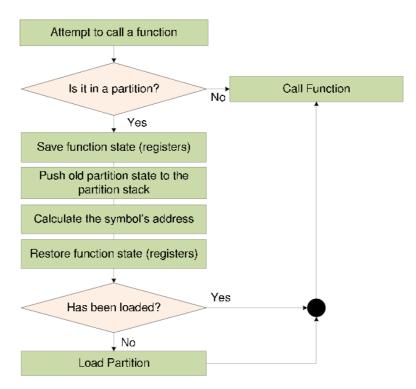

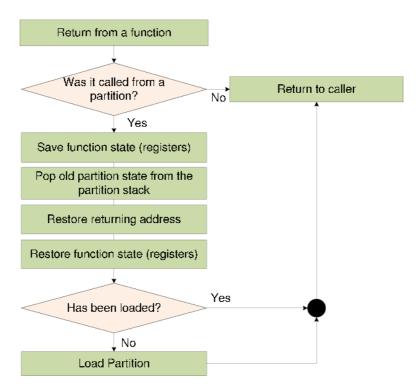

| 4.5 | A Flowchart of the first section of the partition manager call. The logic flow of the initial section of the partition manager kernel. It checks if the partition is loaded and if it is not, loaded and call the function                                                                    | 88 |

| 4.6 | A Flowchart of the second section of the partition manager call. The logic flow of the return part of the partition manager kernel. It checks if the callee partition still exists in memory, if it is not, load it. Return to the caller afterwards                                          | 89 |

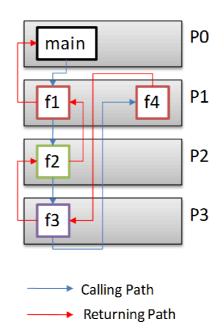

| 5.1 | Partition Manager Function Graph for the Modulus Example                                                                                                                                                                                                                                      | 95 |

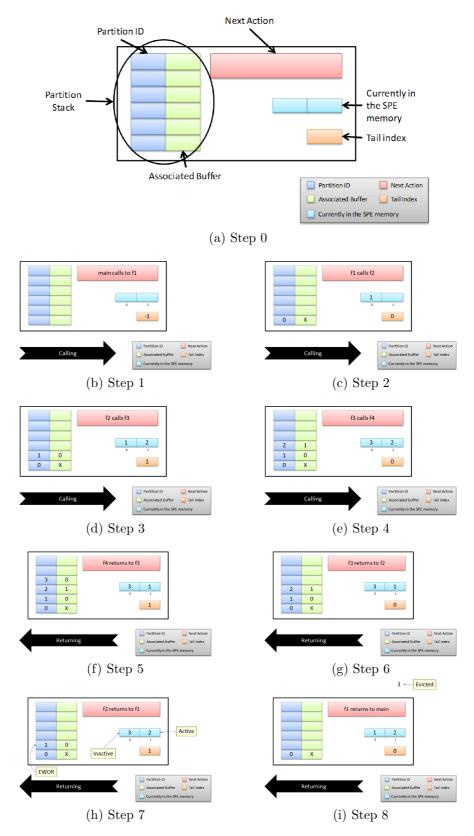

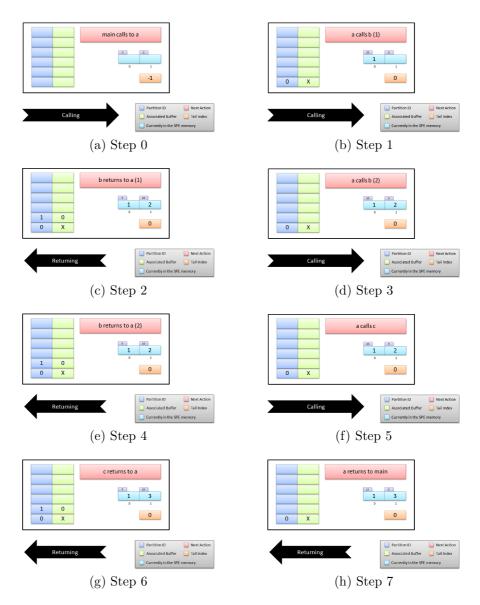

| 5.2 | States of each of the partition manager components across the function calls provided by source code in listing 5.1 using the Modulus replacement policy 96 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

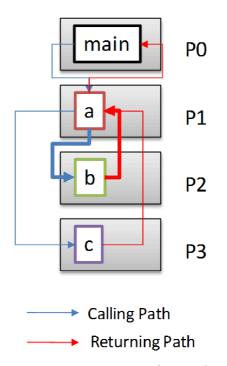

| 5.3 | Partition Manager Function Graph for the LRU example                                                                                                        |

| 5.4 | States of each of the partition manager components across the function calls provided by source code in listing 5.2 using the LRU replacement policy . 100  |

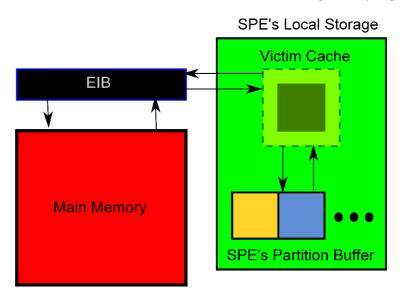

| 5.5 | Victim Cache Framework                                                                                                                                      |

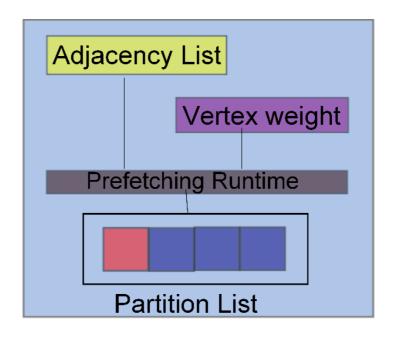

| 5.6 | Prefetching Framework                                                                                                                                       |

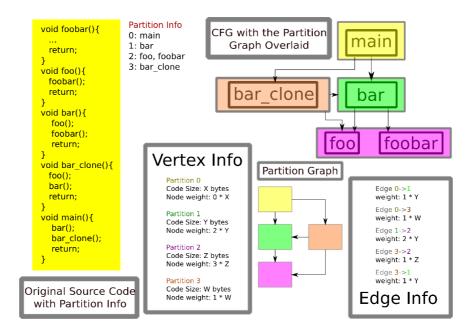

| 5.7 | Creating a partition graph given a piece of source code                                                                                                     |

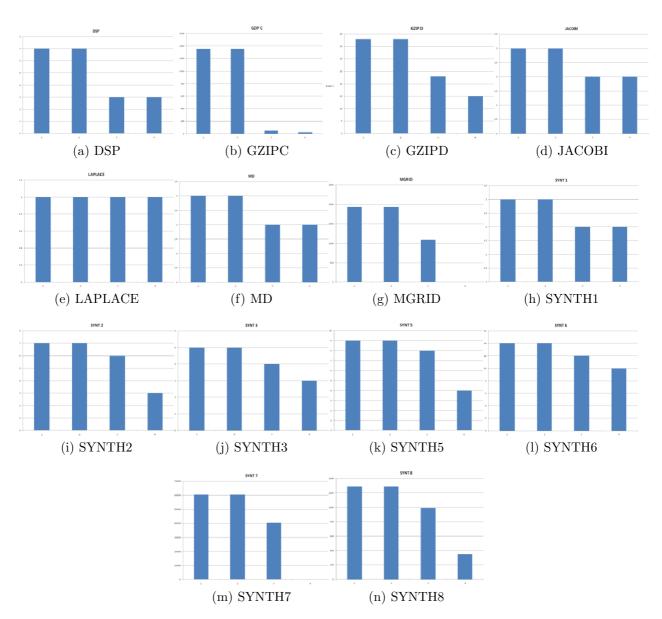

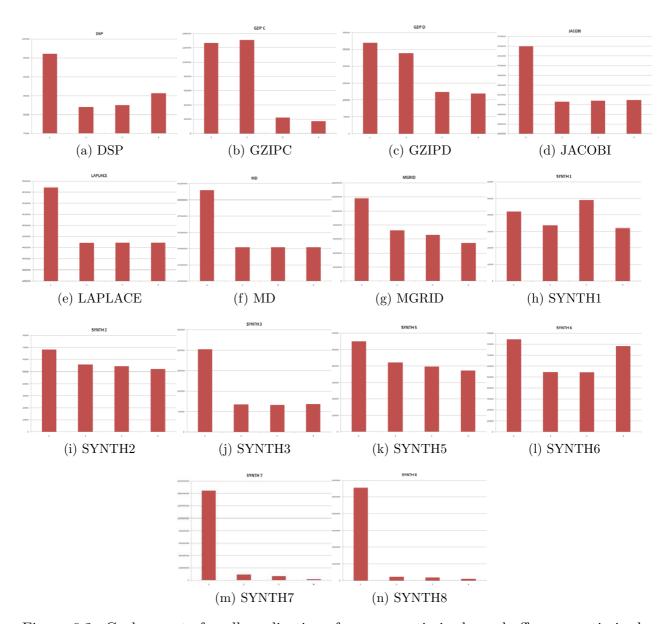

| 6.1 | DMA counts for all applications for an unoptimized one buffer, an optimized one buffer, optimized two buffers and optimized four buffer versions 110        |

| 6.2 | Cycle counts for all applications for an unoptimized one buffer, an optimized one buffer, optimized two buffers and optimized four buffer versions 111      |

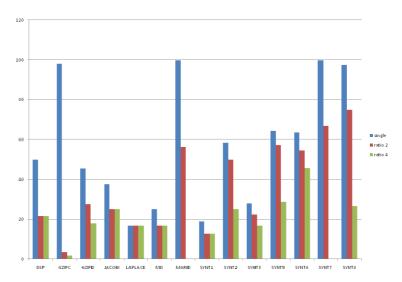

| 6.3 | Ratio of Partition Manager calls versus DMA transfers                                                                                                       |

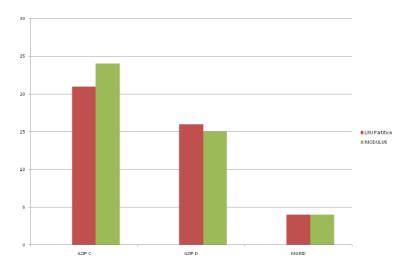

| 6.4 | LRU versus Modulus DMA counts for selected applications                                                                                                     |

| 6.5 | The victim cache comparison with LRU and Modulus policies 112                                                                                               |

## LIST OF TABLES

| 4.1 | Overview of New Assembly Directives      | 72  |

|-----|------------------------------------------|-----|

| 5.1 | The Four States of a Partition           | 92  |

| 6.1 | Applications used in the Harahel testbed | 108 |

### LIST OF SOURCE CODE FRAGMENTS

| 2.1 | Atomic Section's Example                                                  | 30 |

|-----|---------------------------------------------------------------------------|----|

| 3.1 | OpenMP Example                                                            | 54 |

| 3.2 | MPI Example                                                               | 54 |

| 4.1 | Pragma Directives Example                                                 | 70 |

| 4.2 | Linker dump showing the preparation of the partition manager parameters . | 73 |

| 4.3 | Assembly File showing the partitioning directives                         | 74 |

| 4.4 | A Partition Runtime Stack Node                                            | 84 |

| 5.1 | Source code for the 2-buffer example                                      | 94 |

| 5.2 | Source code for the 2-buffer example                                      | 98 |

#### **ABSTRACT**

During the past decade (2000 to 2010), the multi / many core architectures have seen a renaissance, due to the insatiable appetite for performance. Limits on applications and hardware technologies have put a stop to the frequency race in 2005. Current designs can be divided into homogeneous and heterogeneous ones. Homogeneous designs are the easiest to use since most toolchain components and system software do not need too much of a rewrite. On the other end of the spectrum, there are the heterogeneous designs. These designs offer tremendous computational raw power, but at the cost of losing hardware features that might be necessary or even essential for certain types of system software and programming languages. An example of this architectural design is the Cell B.E. processor which exhibits both a heavy core and a group of simple cores designed to be its computational engine.

Recently, this architecture has been placed in the public eye thanks to being a central component into one of the fastest super computers in the world. Moreover, it is the main processing unit of the Sony's Playstation 3 videogame console; the most powerful video console currently in the market. Even though this architecture is very well known for its accomplishments, it is also well known for its very low programmability. Due to this lack of programmability, most of its system software efforts are dedicated to increase this feature. Among the most famous ones are ALF, DaCS, CellSs, the single source XL compiler, the IBM's octopiler, among others. Most of these frameworks have been designed to support (directly or indirectly) high level parallel programming languages. Among them, there is an effort called Open OPELL from the University of Delaware. This toolchain / framework tries to bring the OpenMP parallel programming model (De facto shared memory parallel programming paradigm) to the Cell B.E. architecture. The OPELL framework is composed of four components: a single source toolchain, a very light SPU kernel, a software cache and a partition / code overlay manager. This extra layer increases the system's programmability,

but it also increased the runtime system's overhead. To reduce the overhead, each of the components can be further optimized. This thesis concentrates on optimizing the partition manager components by reducing the number of long latency transactions (DMA transfers) that it produces. The contributions of this thesis are as following:

- 1. The development of a dynamic framework that loads and manages partitions across function calls. In this manner, the restrictive memory problem can be alleviated and the range of applications that can be run on the co-processing unit is expanded.

- 2. The implementation of replacement policies that are useful to reduce the number of DMA transfers across partitions. Such replacement policies aim to optimize the most costly operations in the proposed framework. Such replacements can be of the form of buffer divisions, rules about eviction and loading, etc.

- 3. A quantification of such replacement policies given a selected set of applications and a report of the overhead of such policies. Although several policies can be given, a quantitative study is necessary to analyze which policy is best in which application since the code can have different behaviors.

- 4. An API that can be easily ported and extended to several types of architectures. The problem of restricted space is not going away. The new trend seems to favor an increasing number of cores (with local memories) instead of more hardware features and heavy system software. This means that frameworks like the one proposed in this thesis will become more and more important as the wave of multi / many core continues its ascent.

- 5. A productivity study that tries to define the elusive concept of productivity with a set of metrics and the introduction of expertise as weighting functions.

Finally, the whole framework can be adapted to support task based frameworks, by using the partition space as a task buffer and loading the code on demand with minimal user interaction. This type of tasks are called Dynamic Code Enclaves or DyCE.

#### Chapter 1

#### INTRODUCTION

During the last decade, multi core and many core architectures have invaded all aspects of computing. From embedded processors to high end servers and massive supercomputers, the multi / many core architectures have made their presence known. Their rise is due to several factors; however, the most cited one is the phenomenon called "the power wall." This "wall" refers to the lack of effective cooling technologies to dissipate the heat produced by higher and higher frequency chips[57]. Thus, the race for higher frequency was abruptly stopped around 2006 with the "transformation" of the (single core) Pentium line and the birth of the Core Duo family [51]. For the rest of this chapter, when referring to the new designs, I will be using the term multi core to refer to both many and multi core designs, unless otherwise stated.

Nowadays, the multi core architectures have evolved into a gamut of designs and features. Broadly, this myriad of designs can be classified into two camps. The first one is the "Type One" architectures which describes "heavy" cores¹ glued together in a single die. Designs in this family includes the AMD Opteron family and all the Intel Core Duo line. The "Type Two" architectures refers to designs in which many "simple" cores² are put together in a single die. Most of today designs have an upper limit of eight with a projected increased to twelve and sixteen in the next two years, with designs like Nehalem and Sandy

<sup>&</sup>lt;sup>1</sup> i.e. Cores which have many advance features such as branch prediction, speculative execution and out of order engines

<sup>&</sup>lt;sup>2</sup> i.e. Cores that have simple features such as in order execution, single pipelines, lack of hardware memory coherence and explicit memory hierarchies; however, they may possess esoteric features to increase performance such as Processor in Memory, Full / Empty bits, Random memory allocators, etc

bridge from Intel and AMD's twelve-core Magni-Cours chips (being introduced in late 2011 or early 2012) [5].

On the other hand, type two designs can have processing elements counts of 64 (Tilera-64 [26]), 80 (Intel TeraFLOP Chip [59]), and 160 (Cyclops64 [31]). Their raw computational power allows type two designs to be used in the current super computers which now have enough computational power to handle PetaFLOPS calculations[27]. Examples of both types of designs are given by figure 1.1. It is very common to separate the design only based on the sheer number of processing elements. Thus, designs that have processing elements numbering in the lower tens are considered multi core and the ones above are classified as many core ones.

Although the rise of multi / many cores have brought a new era of computing, due to the massive computational power that these designs provide, they do not come without a price. For type one architectures, the cost of maintaining the advance hardware features does set a very strict limit on the number of processing elements that can be glued together in a chip or coexist in a single machine. This lesson was learned long ago by the supercomputing community.

Most SMP and shared memory designs limit the number of core/processors that can co-exist on a system using shared memory design to around 64 or 128. Using more processors can incur in a disastrous loss of performance due to consistency / coherence actions between the processor's caches and main memory and long latencies between the farthest memory banks[48]. Some companies, like Cray with its T3E, challenged this number by producing systems that were "incoherent" in hardware but have some programming safe nets that provides memory consistency if the programmer requires it[18]. This foreshadows the current trends that are appearing in the market nowadays.

Conversely, type two design's simplicity sends destructive waves upward to the software development stack. Since many of the features that programmers, system software designers and operating systems depended on are gone, most of the software components of current systems require a "re-imagining" of their parts. Problems, such as restricted memory space, ILP exploitation and data locality and layout, which were fixed thanks to these

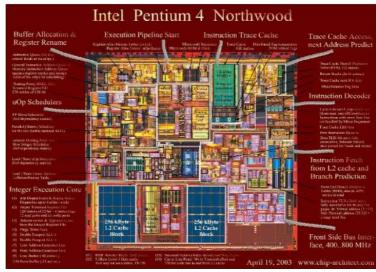

(a) Pentium 4

(b) TeraFLOPS

Figure 1.1: 1.1a Examples of Type two [62] and 1.1b Type one architectures [30]  $\,$

advanced hardware features, have risen anew and are haunting programmers and system software designers alike. This whole collection of problems (plus some classical ones) can be summarized by characterizing the "productivity" of a computer system.

It is a common knowledge that parallel programming is difficult [79]. The easiest parallel programming languages, like OpenMP and MPI, still present difficult problems to the users (both programmers and compilers) such as efficient data decomposition and layout, workload distribution, deadlock / livelock avoidance, priority inversion, effective synchronization, among others. Thus, parallel programming has always been associated with low productivity environments. This has been taken in consideration by major players in the industry, such as IBM, Sun and Cray. An example of the renewed interest in productivity was the High Productivity Computer Systems (HPCS) project[29] funded by DARPA. A discussion about productivity in High Performance Computing can be found on chapter 2. Next, we examine one of the major reasons that multi / many core has become the major force in the market: Power.

#### 1.1 The Power Race and Multi Core Designs

The current generation of programmers is faced with unique opportunities in this new era of multi-core systems. New systems are coming into play which have an increased number of cores but a shrinking of "heavy" hardware features. Such a trend results in a plethora of multi-core machines but a dearth of multi-core environments and languages. This is due to the dependency of many of the low level software stacks to these hardware features. This change came to the mainstream computing at the beginning of this decade (2000's) when chip manufacturers especially, Intel[50], changed their frequency race for multi-core and "green" chips. This move marked the official start of the multi-core / many core era in mainstream computing. This gave the chip manufacturers a free pass to extend their models with more cores and cut off many of the "extra" baggage that many chips had. However,

<sup>&</sup>lt;sup>3</sup> In this thesis, productivity will be defined as the ability to produce sufficiently efficient code in a reasonable amount of time by an average programmer

this also involved a change on the way that main stream computing defines concepts such as productivity[37].

As any computer engineer knows, the concept of productivity seems to be a very fluid one. On one hand, we have performance being represented as code size, memory footprint and power utilization (lower is better). Peak performance is still important but it can take a second place when dealing with real time systems, in which a loss in performance is acceptable as long as the quantum interval is respected. On the other hand, High Performance Computing (HPC) plays a completely different game. On these systems, the total number of Floating Point operations per second (FLOPS) is king. These systems and the applications written for them are created to exploit the most of the current technology to reach the next computational barrier. As of the writing of this thesis, this barrier stands on the PetaFLOPS (10<sup>15</sup>) range and there are many proposals to reach the next one (Exa) in the not-so-distant future [78]. However, HPC, in particular, and the rest of the computing field are changing. In HPC, and the general purpose field, another metric is being added: power. Power was one of the major factors that put the nail in the coffin of the Pentium-4 line. To gain a bit of perspective, we should take a view at features that made the Pentium-4 such a power-hungry platform.

#### 1.1.1 The Pentium Family Line

One of the perfect examples of the power trend is the Intel family of microprocessors. The first Pentium microprocessors represented a jump in the general purpose processors. They offered advance features such as SuperScalar designs<sup>4</sup>, 64 bit external databus, an improved floating units, among others. However, this also started the famous frequency race in which all major manufactures participated. In the case of Intel, all the iterations of their Pentium family show an almost exponential increase on frequency from its introduction in 1993 to 2006, as represented in figure 1.2. The Pentium line spanned three generations of hardware design. These are the P5, the P6 and the Netburst architecture. The evolution on these designs was represented by the addition of several features to increase single thread

<sup>&</sup>lt;sup>4</sup> Dynamic multiple issue techniques using principles presented in [80]

performance. One of the most cited features is the extension of the pipeline (later christened the hyper-pipeline) and the introduction of SuperScalar designs (e.g. the out of order engine)<sup>5</sup>.

Figure 1.2: Intel Processor frequency growth from 1973 to 2006

The hyper-pipeline represented an increase on the number of stages of the normal execution pipeline. This grew from 5 for the original Pentium to 14 on the Pro to 31 on the Prescott core. This change had a tremendous effect on hardware design. First, it allowed the frequency to jump up between designs. Second, the cores must be able to reduce the amount of pipeline's flushes that occur since they represent the greatest performance degradation factor due to flushing such a long pipeline. For example, on a typical code in SPEC, there is a branch every four to six instructions[53]. If you have a 31 stage pipeline, it will be continually flushed and stalled<sup>6</sup>. Third, a longer pipeline has an average lower Instruction Per Cycle (IPC) than a shorter one. Nevertheless, the lower IPC can be masked by the higher operating frequency and the extensive hardware framework inside the cores.

<sup>&</sup>lt;sup>5</sup> Due to Intel's secrecy about the designs of their cores, the following information was extracted from [39] which was extracted using a combination of micro-benchmarks, white papers and reference manuals

<sup>&</sup>lt;sup>6</sup> This is a very simple example since each instruction in the Pentium Core is decoded into several micro operations and the reorder buffer, simultaneous multi threading and the branch prediction will keep the pipeline busy, but the idea still holds

Due to the branch cost, Intel engineers dedicated a great amount of effort to create very efficient Branch predictor schemes which alleviate the branch costs. Some basic concepts need to be explained. When dealing with predicting a branch, two specific pieces of information need to be known: do we need to jump and where to jump to. On the Intel architecture (even in the new ones), the second question is answered by a hardware structure called the Branch Target Buffer. This buffer is designed to keep all the targets for all recently taken branches. In other words, it is a cache for branch targets. The answer for the former question (i.e. do we need to jump) is a bit more complex to explain <sup>7</sup>.